很多高手都搞不定的约束,求大神解答。

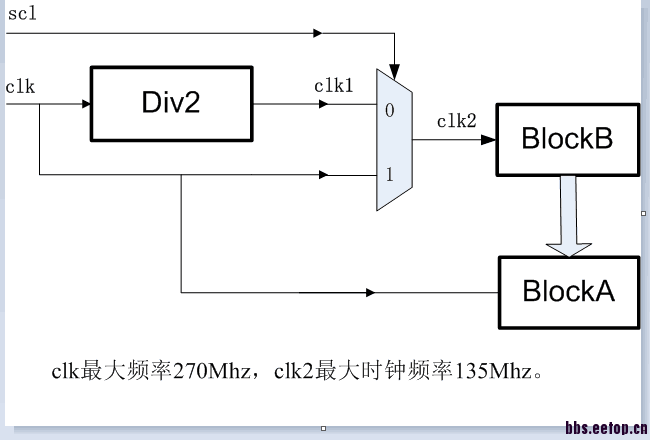

一般情况下可以在CLK 和CLK1分别generate两个时钟,然后让综合器自己分析,但是现在的设计是CLK如果超过135M,CLK2就会选择CLK1,只有低于135M时才会是从CLK直通到CLK2,请大神搭救,多谢!

按严的约呗

但是现在的设计是CLK如果超过135M,CLK2就会选择CLK1,只有低于135M时才会是从CLK直通到CLK2? 不是很理解啊 ,不建议设置generate clk1, 因为没有直接的FF, clk2 建议 divide by 1-source MUX/I1,因为这是它的最高频率,再resynthesis 一下 应该就ok了

其实如果综合的话,可以直接在Clk2处从Clk1 generate时钟,这样Clk2频率为0~135,且与Clk为同源时钟;但是CTS后这个约束怎么处理倒是有点麻烦

或许你可以分两种情况进行约束:

# 1. CLK<135M:

create_clock -name CLK_low -period [expr [1000/135] [get_ports clk]

create_generate_clk -name clk2_low -combinational -source [get_pins MUX/in1] [get_pins MUX/out]

# 2.135M<CLK<270M:

create_clock -name CLK_high -period [expr [1000/270] [get_ports clk] -add

create_generate_clk -name clk1_high -divide_by 2 -master CLK_high -source [get_pins Div2FF/CP] [get_pins Div2FF/Q]

create_generate_clk -name clk2_high -combinational -source [get_pins MUX/in0] [get_pins MUX/out] -add

# At the same time

set timing_enable_multiple_clocks_per_reg true

# And set other constrains like dont touch and uncertainty

在clk端创建两个时钟:clk_270和clk_135;

在Div2创建一个生成时钟:clk_270_div2,Master是clk_270;

在Mux的1端创建一个Combinational生成时钟:clk_135_gen ,Master是clk_135 (目的是把clk_270透过这里的路径打断)

至此,clk2上只能出现clk_270_div2或者clk_135_gen的时钟,即不会出现大于135M的时钟。

最后,由于clk只能是270或135二选一,我们需要创建两个physically_exclusive的Clock Group:{clk_270*}和{clk135*}