求DRC关于metal slot违例解决方法?

小弟做DRC验证完后,每层金属都有metal slot违例;

请问metal slot是在icc哪一步完成的,因为我好像没看到进行metal slot的指令;

DRC对于这种违例,一般采取什么样的方法?

谢谢!

最后一步,

电源线不要画的太宽,

还请解释详细一点,

最后一步,具体哪条指令?

metal slot 密度不够跟电源线宽度有什么关系吗?metal slot 不是用于金属过大所以才开slot吗

谢谢!

从开始就不用超宽的metl不就规避过去了么?

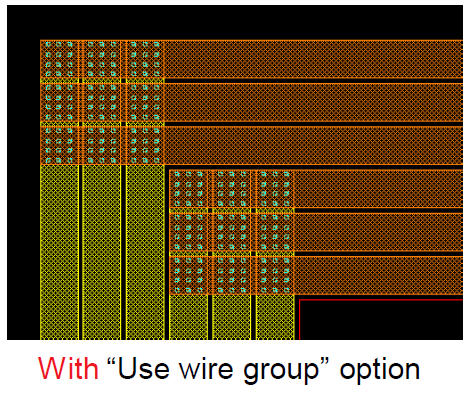

wire group的形式不也一样么?

做slot属于自找麻烦类型的,呵呵

谢谢小编回答!

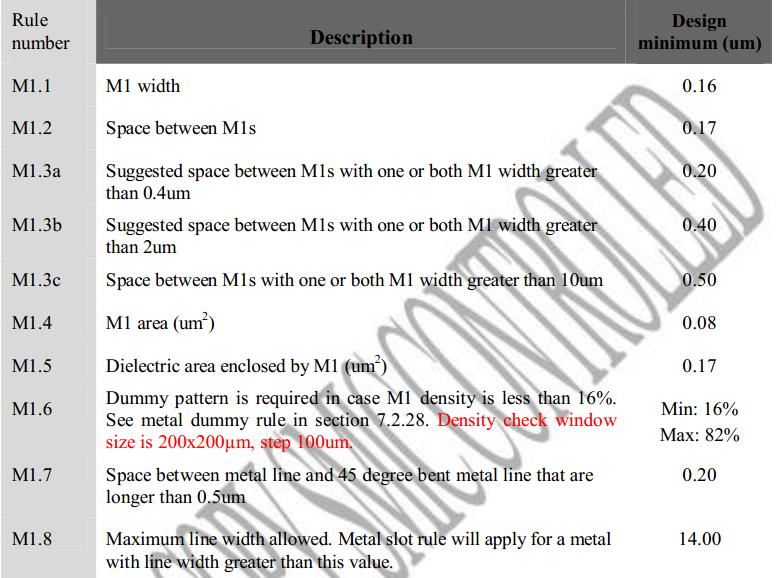

弱弱地问个问题:根据tf文件已经规定了金属宽度,那为什么会有一些宽度很宽的金属呢?(参考工艺DRC规则文档部分金属层1规则,见下楼附图)

另外wire group这概念第一次接触,还请赐教;

slot这个是附图里的M1.8规则里要求的,这个工艺厂里提供的DRC那个ev文件也就有这项规则检查了。

附图

因为规定的是最小的线宽。

楼上正解

谢谢!

举个例子:

输出的电流为45mA,双层金属M1的电流密度为1mA/um,M2的电流为1.5mA/um,金属宽度超过30um就需要使用Slot。

如果仅仅用M1连线,如果用两根M1,每根就只需要22.5um的宽度。

如果仅仅用M2连线,如果用两根M2,每根就只需要15um。

如果使用两层金属走线,可以M1和M2的金属线宽度都可以控制在30um以下。

以上几种情况都可以避免使用slot(应该就是wire group)

上图就是wire group的一种,这是VSS VSS VSS VDD VDD VDD的方式,当然也可以VSS VDD VSS VDD VSS VDD的方式。这个就随意了。

如果面积比较紧张也可以采用多层金属cover的方式避免slot问题

学习了,谢谢楼上两位!

命令:slot_wire

小编,请教个问题哈,如果面积比较紧张,为了面积考虑,采用更多层金属cover,应该如何来做floorplan?我每次生成的版图都是ring在core周围生成,如果遇到了面积过大的时候,只能通过删减逻辑来减小面积,从而能够在给定的面积里放下版图。希望小编赐教哈非常感谢!

power ring是不是在core周围这不是重点,重点是你的供电够不够。不知道我这样说你能不能理解。power plan的做法这不仅跟你的供电的点有关系,还跟你用到的金属层数有关系,你可以灵活应对。

有没有ring不是重点,ring是不是在core周围不是重点,它也可以在core区域内,类似于stripe。哪些地方的power的metal应该宽,哪些地方应该窄,这和供电的点有关系,ring并不是四边一定要一样宽的。

当然你采用几层metal重叠的方式也是一个办法,总之不同的设计,根据具体情况多考虑几种可能性,只要供电没问题了,剩下的就是你自由发挥了。

非常感谢小编的详细答复!那么再考虑到供电的同时,出于面积的规定,我想要把ring做在core内,而不是core的周围,这样就可以使density减小,更容易布线,具体应该如何来操作呢?我是一筹莫展,始终无法实现,还望小编赐教,在此先谢过了!

addRing或者手画都行,记得手画前把属性改为ring

小编,我是在gui操作,add ring,但是把各个设置都试了下,不是ring没有出来就是出来就是在core的周围,无法让它在core内生成,卡在这无法继续了,非常紧急啊,还请小编指教一下如何操作。谢谢!

gui下面一样,offset设置为负值就行了。

也可以用那个user define coordinate,用鼠标选择坐标,或者手动输入坐标都行

出于面积的规定,我想要把ring做在core内,而不是core的周围,这样就可以使density减小,更容易布线,具体应该如何来操作呢?

这句话什么意思?我没太理解为什么放在core 内就能够使density 减小?

如果要画在core 内用gui 界面指定的坐标点在core 内不就可以么?

可能是我表述的不清楚,比如面积是1000*500,那么如果offset为25,25,25,25,此时core的实际面积就会有950*450,这样布局布线的面积不就减小了,从而density不就会变大了吗。

呵呵但是你片子还是真么大啊所谓的density增加也不属于节省了面积。不过就算你做了ring,ring下面也还是放cell 和走线的啊。ring 你也只是用了基层高层金属吧

呵呵,如果offset是正值的话,encounter是不会在环的下面放cell的。

为什么设置了正值不会放cell?下面也有power railwelltapendcap都可以放啊。你说不可以放 是工具设置了offset 工具就不让放还是认为的不放?

如果设置了offset为正值后,电源环就会在实际放cell的core的四周生成,而且四周的环的金属下面没有放任何cell,cap or filler。

ok那我想问一下那chip 四周的边界要加的endcap和wellltap 都加在哪里?

ICC里面直接Preroute > Slote Wires就可以了,或者用命令slot_wire

可不可以理解为就是打了几个特别长的slot,将一条宽金属线拆分成几条并联的窄金属线?