求助,下图中的时序约束在dc中如何实现

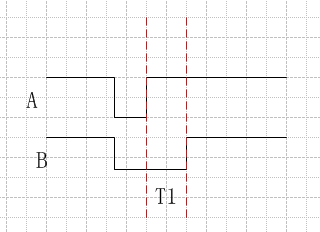

有两个信号A B,是模块digit的输出,通向一个IP,从IP的手册上查到一个时序,需要A和B两个信号的波形如图,

图中的时间T1,必须在0到10ns之间。

前端设计时,由于外界的时钟频率为74ns,因此在代码上设计是将T1处理为零,但是通过PR后的sta/sdf,后仿,发现T1的时间不满足这个要求。

想问问,dc在综合约束的时候,要如何约束这个AB信号,目前dc中没有对两个端口进行约束

问题补充,AB两个信号之间没有时序路径;且AB是输出向一个IP的控制信号,IP在设计中已经做成BLACK BOX

max/min delay

可否使用set_data_check?

set_max/min_delay似乎只能对组合链路做约束,而且AB信号之间没有时序路径,约束set_max_delay -from A -to B似乎不太合理

可否使用set_data_check? ==》可以试试,不过后端不一定认这个命令

约束set_max_delay -from A -to B似乎不太合理 ==》不是这么做的,多找几个set_max_delay 的实际用法学学

set_max_delay -rise_from digit/A -to IP相应端口X

set_max_delay -rise_from digit/B -to IP相应端口X+10

试试看行不,呵呵。

恩,不过,digit直接就把这两个信号输入到IP上的,中间也没有什么链路,之间就是组合逻辑,所以我觉得这个方法有点悬,不过值得一试,谢谢

这个光靠约束是完不成的,加约束的最终目的是为了在路径上加延时,如果这样的话那么A和B的上升沿可能会发生变化,所以最简单是在B上加逻辑吧!个人愚见

此法不行。

你的意思是在dc得到的网表中,给B的端口加上一个delay_cell么?

小编,我还是没想明白如何通过set_max_delay的方式来加约束,不能给简单的说下思路?

就是mnluan的做法,要加上min delay

学东西要会举一反三,综合总结。

小编的意思是用set_max_delay和set_min_delay来约束A和B的时序,不过我认为不太可行

哈哈,还是小编理解我啊。因为看小编不理解set_max_delay的实际用法,所以写了两句,提供个思路。

对于这个问题,我是这样考虑的,

set_max_delay -rise_from digit/A -to IP相应端口 X

set_min_delay -rise_from digit/A -to IP相应端口 X-5

这两句是想把digit/A到IP的延时控制在 (X-5, X) 之间。

set_max_delay -rise_from digit/B -to IP相应端口 X+5

set_min_delay -rise_from digit/B -to IP相应端口 X

这两句是想把digit/B到IP的延时控制在 (X, X+5)之间。

然后最好情况是两条路径延时都为X,延时差为0, 最坏情况两条路径延时差X+5 - (X-5)=10。

twn2000兄,能否说说,你认为不可行的原因。

不管用什么样的命令,工具最终实现就是加减buff或者INV吧,可以看到只有上升沿有约束,如果要实现的话只能加input和Out的transition不一样的buff或inv,10ns我认为不太容易实现,个人愚见!

本人认为不能使用set_max/min_delay命令,该命令是用来约束有数据通路的两个点之间的延时的,而小编所说的A、B之间根本没有数据通路。我认为应该使用set_data_check命令。

重新尝试了下max/min delay,虽然和你的解法不太一样,但是最后还是做到了AB的时间差为3-7ns

非常感谢你的帮助。

AB之间确实没有数据通路

使用set_max min delay的目的不是约束数据通路,而是约束各自到IP接口的路径,

还想补充一下

如果仔细看这个时序图,会发现,AB的fall edge是平齐的(或者可以理解为有一定偏差和余度),如果使用set_max min在保证了T1的时间情况下,想要保证AB的fall edge的时序要求,即使可行,想必也是较为复杂的

但如果使用set_data_check,AB路径的时序约束就会非常简单

至于PR工具认不认这个命令,我还具体确定过,我只是在encounter中敲入了这个命令,没有警告和error,如此看来似乎这个命令PR工具可以认。

嗯,是这样的。上升沿要错开,下降沿又要平齐,这个很难。twn2000担心的也就是这点吧。呵呵,我当时主要关心的是如何用set_max/min_delay来约束AB上升沿的关系。

set_data_check 在encounter中是可以识别的,我用过。对于这样的路径也可以用set_data_check来约束, -setup 和 -hold都需要设置。

小编能不能看看加了约束以后在AB的路径上各有什么变化啊?比方说加了什么buff,什么类型等等

插了库里面的两个DEL buffer,让最小时间为3ns,最大时间差为7ns。和约束一致了。

加了Buff后,下降沿差多少啊

下降沿的其实在我的应用中是没有考虑的

我没有报过这个下降沿的延时,我只报了-rise_from,不过我想应该是和rise_from差不多。

如果真的说要求下降沿也有特定的要求,当然是需要使用set_data_check命令,与你说的一致。

非常感谢你的帮助和解答

OK,谢谢讨论

谢谢回帖!

你好,请问下,我想在encounter下报告这个路径的hold时序,但是我用report_timing -unconstained -from A -to IP/A的命令,得到的是max的时间,想问问如何得min时间,我想一定是这个命令要加什么argument才行,谢谢了。

-early

大神厉害啊!

use set_data_check to constraints the skew between the rising edge of both signals

P&R tool can acknowledge this setting