如何画seal ring 和 scribe line 有酬谢

smic18 工艺

有酬谢

15711123392

designrule上都有写啊 scribeline不需要你画啊

根据具体工艺厂,design rule 里面有推荐的结构和尺寸。

sealring 一般(P sub 工艺)加P注入的环 加金属环加接触孔/通孔环,大部分工艺还会加入pad 层次做一个开窗的环,有需要还可以加倒角。

scribe line一般可选80u 或60u 具体看工艺厂流片时 在scribe line 放什么东西和怎么放,封装厂划片时一般都能支持60u

请仔细查看design rule 每个工艺的 sealring 都有不同的设计规则。一般画法都很相似。

看了design rule。

但还是希望有个例子看看才放心

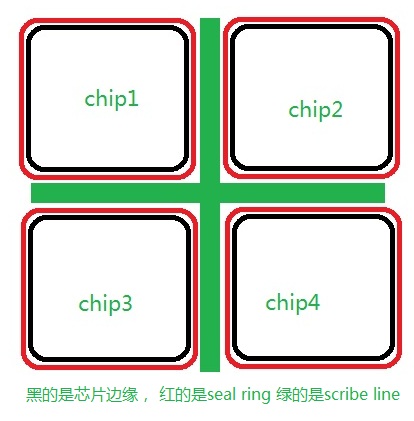

我们是5mmx5mm的 放4颗。

fandury 只管最外面的环。

4颗的内部的scribe line 需要自己画

我是希望有个例子。这样比较放心

1、最外面的环?是什么环?2、scribe line是预留的划片间隙,60um-100um左右,不需要制作。

3、详细的东西最好和foundry问清楚,一般foundry会提供带sr的pdk,如果没有按照rule画就好了,没啥难度。

就是这样,请看看图

走mpw, faundry 要求画成这样。

他会在最外面加seal ring

和 scribe line。

给你的芯片就是如图的。

你自己再找封装厂再切成4个。

有人说scribe line 要画些东西。

这样切割的时候就不容易裂到芯片。

是这样吗?

pad应该是必须的,其他的不知道!

关于SealRing,DesignRule中有详细的介绍,你可以自己按照DesignRule去画就好了,

或者是可以让Foundry给你加上;

ScribeLine只是两颗die之间的Space,里面包含SealRing或测试的buffer电路,一般不需要我们自己去做。

关于这个问题,其实有点难搞。其实fab有自己对应的scribeline rule,lz可以去问问看。一般有蛮多层次是为了划片方便而加的比如OD比如cover如果是clear极性也会加上,还有一部分比较关键:比如dummyblock,如果不加这层,如果是先进工艺,很可能最后这块区域会堆满dummy,那么最后划片的时候会损失多少把刀呢。真的不建议lz自己添加scribeline,对后期划片很不利;但是fab又很不想动客户的芯片数据,因为很容易动到数据检查不出来,逃避责任吶。

还是建议lz让fab帮你加,或者为什么不直接提供四个数据让他们去规划呢~之后只要让他们提供4颗die就好了呀。

仅供参考。