metal cap mom结构

各位路过的大牛们,向大家请教一个问题:由于foundry没有提供mom电容,现在自己要手动新建metal cap,我想问问大家这种结构有多少种,结构是怎样的,希望大家给予指点,感激不尽,谢谢!

我自己做了一个metal cap,学着编写了一下cmd file,run lvs总是提示无法识别layout,自己定义的dummy layout用来识别却总是没反应,请问大家有什么办法解决这个事情吗?谢谢!

由于foundry没有提供mom电容

看看有沒有 MIM 電容

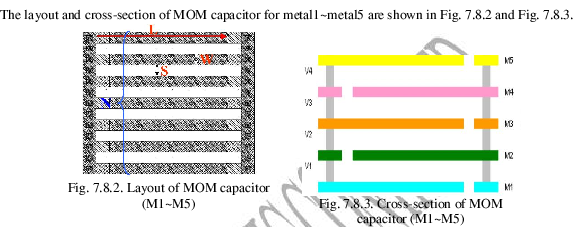

結構方面 有多少M就放多少M

做成交指狀 連側面電容都用上

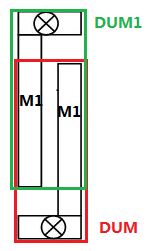

foundry也没有提供MIM电容,我很想知道自己手工的mom结构除了插指,还有平板电容么?同层金属间的,不同层金属间的考虑么?比如M1和M1 M1和M2 谢谢

插值没model、平板缺一层。估计没戏。

M1 M2 重疊部分

M1 M1 間只有側面

所以會做交指式

讓上下左右都有電容

谢谢您的答复,我也只想到了这两种方法!现在就要自己学习写cmd file识别这些了

向您请教一个问题,cmd file中我已经定义了自己的上下极板的layer,就是run lvs的时候,总是提示没有layout,device不能被识别,我在tf中定义了识别层,也在lvs.cmd中定义了map layer,您知道怎么才能让device被识别吗?我翻阅svrf看了半天没看到关键词,请帮忙指点一二,谢谢!

你可以參考 mos 怎麼寫

device 是 關鍵字 ,在 卡利伯 預設中並無分大小寫

某層 = 識別層1 + 識別層2

device metalcap某層 上板層 上板層 w L ...

資料那邊有一個 敎寫 command file 的,可以參考

device metalcap某層 上板層 上板層 w L ...

寫錯ㄌ應該是

device metalcap某層 上板層 下板層 w L ...

感谢您的回答,我也是这么做的,可是run lvs就是提示cells not be identified,Nothing in layout!

我是这么设置的首先我在TF中定义了5层layer DUM,DUM1~DUM4。在LVS中添加对应的layer MAP,我想做m1和m1间的插值电容MCAPX1,上极板MTP1使用DUM1和M1识别,下级板MTN1使用DUM和M1识别,电容识别layer MTL:DUM1 AND DUM; m1m2叠加在一起与m1m2叠加在一起间的电容MCAPX102,上级MTP102:DUM1,DUM2和M1,M2 ,下级MTN102:M1 M2 DUM,简单编写如下:

1) MTP1=metal1 AND DUM1 ,MTN1=metal1 AND DUM,MTL1=DUM1 AND DUM

2)MTP102=(metal2 AND MTP1)DUM2 ,MTN1=metal2 AND MTN1,MTL102=MTL1 AND DUM2

DEVICE C(MCAP1)MTL1 MTP1(POS)MTN1(NEG)【1.0 0】

TRACE PROPERTY C(MCAP1) C C 0

DEVICE C(MCAP102)MTL102 MTP102(POS)MTN102(NEG)【2.0 0】

TRACE PROPERTY C(MCAP102) C C 0

【】其中的值时自己随便定的,暂时不考虑这个

谢谢指点!

MTP102=(metal2 AND MTP1)DUM2 這可能有問題

MTN1=metal1 AND DUM

MTN1=metal2 AND MTN1

這可能有問題

DEVICE C(MCAP1) MTL1MTP1(POS)MTN1(NEG) netlist element "X"

主體是 MTL1

感谢您的答复,我调整了一下编写,关于M1和M1间的插指Metal CAP 有两种写法:

1) MTP1=(metal1 AND DUM1)NOT DUM ,MTN1=(metal1 AND DUM) NOT DUM1 ,MTL1=DUM1 AND DUM

2) MTP1= (metal1 INTERACT DUM1)NOT DUM ,MTN1=(metal1 INTERACT DUM) NOT DUM1 ,MTL1=DUM1 AND DUM

上面两种写法 run lvs 均可识别,把上面的识别层MTL1写成这样也可以过ML1=(DUM1 AND DUM)INTERACT (MTP1 OR MTN1)。

但我想了想按照上面两种写法 也没有区分出哪是上下级,MTL1也就DUM和DUM1做运算了感觉不出有多大差别,烦请您帮我指点一下差异,谢谢!

恭喜成功了

不管黑貓白貓,會抓老鼠就是好貓

能運用即可,先有再優化

同是M1層也就沒什麼,上級版,下級板

我會這樣構思

在 MCAP 中做出 mc1_plus 和 mc1_minus 當做pin點

讓m1mc1_plus 和 mc1_minus 相互 能connect

如同 poly connect polygate

感谢你的答复, 现在我就用自己能实现的方法继续进行。我想用DUM2和DUM两层辅助来区分MCAPX2和MCAPX102,但就是不成功!您有么有办法比如说:DUM2i=DUM1 AND DUM2当做一个新的层次配合DUM来识别MCAPX102,我这样做也不行。不知道怎么能让DUM2i和DUM2一样使用 谢谢答复!

有2個想法給你參考

1. m1 m2 交叉式

這樣是一個電容或是多個電容並串聯

2.dummy layer的獨特性

dummy2ii = dummy2i not dummy2

會不會又有重疊dummy1的疑慮

最近在玩撲克牌 如同 烏龍的機率

=全部 not 同花順 再 not 4 條 再not full house ......

感谢您的答复,我现在已经写出了部分。看designer的要求,要是没问题 我这版就写好了十分感谢您的指点 谢谢!

真是恭喜了繼續加油

DEVICE [DEVICENAME] [DEVICEAREA] [TERMINAL1,TERMINAL2...]

[PROPERTY X1,X2

X1=..

X2=..]

TRACE PROPERTY [X1,X2...],[X1,X2...] ratio

完成器件区域识别和端口识别就可以,器件的端口不能重复定义和使用。电容的话一般用AREA做特征值,MOM一般都是建立在MIM上的叉状结构来提高容值和线性度。我做的rule里面几乎没有提供MOM电容的典型值。

nicer

thx

thank you

这里是用总面积来计算电容值的吗?公式中的0.9是什么呢?

是用面積算的 通常也考慮 串並聯效應

0.9 我猜是經驗累積 , 得到的參數

1.先确认你的LVS rule中是否定义了MOM device,如果定义了,则按照rule画

2. 如果LVS rule中没有定义,则最好问下foundry,不然自己画有风险的

very good,多謝。

自己做MOM電容,跑LVS時在Schematic裡面不放symbol就不會出現LVS問題了吧,因為此時MOM電容與metal連線無異。