详解FPGA开发流程中每一环节的物理含义和实现目标

必需的信号TDI, TDO, TMS和TCK以及1个可选信号TRST构成,其中:

TDI,用于测试数据的输入;

TDO,用于测试数据的输出;

TMS,模式控制管脚,决定JTAG电路内部的TAP状态机的跳变;

TCK,测试时钟,其他信号线都必须与之同步;

TRST,可选,如果JTAG电路不用,可以讲其连到GND。

FPGA开发—固化

第二部分固化程序到存储器中的过程可以分为两种方式,主模式和从模式。主模式下

FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程;从模式下则由外部计算机或控制器控制配置过程。主、从模式从传输数据宽度上,又分别可以分为串行和并行。

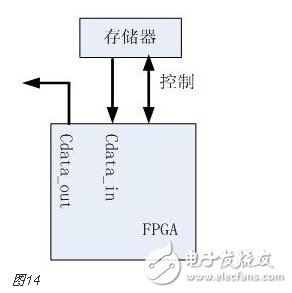

(1)主串模式

主串模式是最简单的固化模式,如图14所示,这个模式过程不需要为外部存储器提供一系列地址。它利用简单的脉冲信号来表明数据读取的开始,接着由FPGA提供给存储器时钟,存储器在时钟驱动下,将数据输入到FPGA Cdata_in端口。

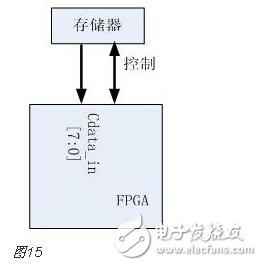

(2)主并模式

主并模式其实和主串模式的一样机理,只不过是在主串的基础上,同周期数内传送的数据变成8位,或者更高,如图15。这样一来,主并行相比主串行的数度要优先了。现代有些地方已采用这种方式来配置FPGA的了。

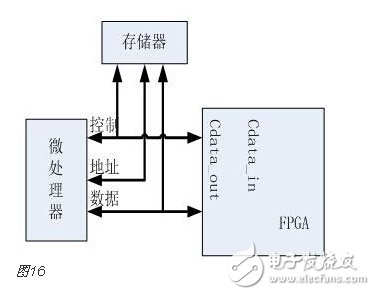

(3)从并模式

从上面看到,主模式下的连接还是很简单的。但是有时候,系统可能用其他微处理器来对FPGA进行配置。这里的微处理器可以指FPGA内嵌的处理器,比如说Nios。微处理器控制着何时配置FPGA,从哪读取配置文件。如图16,这种方式的优点是处理器可以灵活随时变更FPGA配置,同时配置的速度也快。微处理器先从外部存储设备里读取一个字节的数,然后写到FPGA里。

(4)从串模式

理解了从并模式,从串模式就不用很多解释了,它的特点就是节约FPGA管脚I/O。

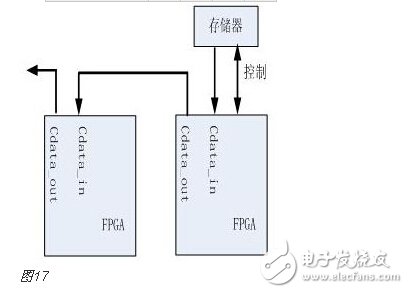

(5)多片级联

多片模式有两种,一种是采用菊花链的思想,多片FPGA共享一个存储器,另外一个是可以使用其他存储器配置不同的FPGA。如果所示是一个共享型的结构,显示启动了。这里分主FPGA和从FPGA,主FPGA和存储器是使用串行主模式来配置,而后面那个的配置是通过第一配置好的FPGA上微处理器进行协调的。

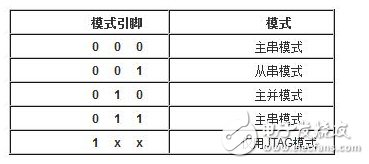

模式选择

现今FPGA应该可以支持上面五种配置模式,是通过3个模式引脚来实现的,具体的映射如下表,在今后模式还是有可能增加的。

在PS模式下,如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号。一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序。只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上。或者配置芯片就是可以方便取下焊上的那种。这样出了问题还可以方便地调试。。

对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K一般在做FPGA实验板的时候,用AS+JTAG方式,这样可以用JTAG方式调试,而最后程序已经调试无误了后,再用AS模式把程序烧到配置芯片里去。

FPGA开发—开发工具总结

在围绕图1把FPGA开发流程讲完后,这里对每个环节中设计的相关软件进行总结,如下表所示。毕竟充分利用各种工具的特点,进行多种EDA工具的协同设计,对FPGA的开发是非常重要的。充分利用了这些EDA工具的优点,能够提高开发效率和系统性能。

表中列出的每种EDA工具都有自己的特点。一般由FPGA厂商提供的集成开发环境,如Altera Quartus II和Xilinx ISE,在逻辑综合和设计仿真环节都不是非常优秀,因此一般都会提供第三方EDA工具的接口,让用户更方便地利用其他EDA工具。为了提高设计效率,优化设计结果,很多厂家提供了各种专业软件,用以配合FPGA芯片厂家提供的工具进行更高效的设计。

比较常见的使用方式是:FPGA厂商提供的集成开发环境、专业逻辑仿真软件、专业逻辑综合软件一起使用,进行多种EDA工具的协同设计。比如Quartus II+ModelSim+FPGA Compiler II,ISE+ModelSim+Synplify Pro等等。

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)