FPGA和功能强大的DSP的运动控制卡设计

一、引言

使用激光雕刻和切割,过程非常简单,如同使用电脑和打印机在纸张上打印。您可以在Win98/Win2000/WinXP环境下利用多种图形处理软件,如CorelDraw等进行设计,扫描的图形,矢量化的图文及多种CAD文件都可轻松地"打印"到雕刻机中。唯一的不同之处是,打印将墨粉涂到纸张上,而激光雕刻是将激光射到木制品、亚克粒、塑料板、金属板、石材等几乎所有的材料之上。

体现激光材料加工的发展水平有三个方面的因素:第一是激光器技术,即应用于激光材料加工的激光器件技术;第二是激光设备加工的机械、控制系统等,即激光加工设备;第三是激光加工工艺水平。

目前,国内专门生产激光雕刻设备的厂家很多,他们竞争已由激光器技术转向对激光设备和加工工艺的有效控制,能否有效解决如下问题:三维图形多轴联动、高速激光扫描和快速推进引起的振动、扫描幅面大小和扫描精度、激光的同步扫描和往复扫描错位、复杂算法和规则图形插补问题等,已经成为竞争的关键。

二、基于DSP和FPGA的设计

针对上述各种问题,结合多年运动控制的经验,我们设计了基于资源丰富的FPGA和功能强大的DSP的运动控制卡——MPC03,在激光雕刻调试中,成功的解决了上述各种问题。

1、MPC03卡简介

⑴ DSP从主机接收运动指令或运动指令块,并把从主机读取的大量图形数据实时的写入FPGA的RAM区,并向主机发送运行状态:位置、I/O状态等;

⑵ FPGA芯片根据接收的指令,完成多轴电机的运动控制(二维图形为两轴,三维图形为三轴):位置、速度、插补、PID调节等;

⑶ 在运动过程中,FPGA同步读取RAM区的图形数据,根据不同的‘0’或‘1’状态,实时地 决定是否开关光,而且并行处理与运动有关的外部I/O信号和通用I/O信号。

⑷ MPC03卡性能指标如下:

最高脉冲输出频率FH:15MHz

脉冲输出频率范围F:0.002~15,000,000 Hz

最小分辨率Mmin :0.002

脉冲频率设置步长R :1~8191

定位脉冲数范围R0 :0~4,294,967,295

自动降速点设置范围R6 :0~4,294,967,295

增减计数器设置范围R10:0~4,294,967,295

2.MPC03卡设计和功能实现

⑴ 硬件电路设计

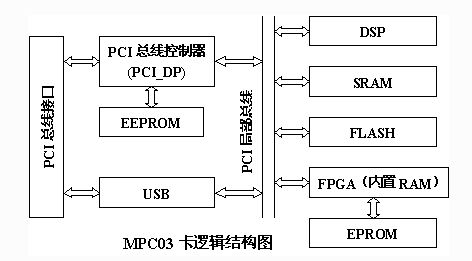

在MPC03卡中主要有DSP、FPGA两个功能芯片,在DSP周围扩展了多个FLASH和SRAM来存储程序和数据,每两个FLASH和SRAM可以共用一个片选信号CS,组成高低双字32位数据总线进行读写,可以提高DSP与MEMORY的通信速度,同时为FPGA配置了一个EPROM来存储下载的程序。本文提到的DSP和FPGA都是低能耗、低电压操作,I/O信号电压是3.3V,而内核电压是1.8V,所以配置了能同时输出3.3V和1.8V两种电压的电压调整器。请参照MPC03卡逻辑结构图。

FPGA资源充足,性价比高,能现场重复多次编程,可以针对不同的小批量客户的具体要求,灵活地修改设计。USB接口可实现脱机工作,不必为每块卡配置一台PC机,工业现场使用方便,成本低,符合时代发展趋势。

⑵ 解决问题的方案

由于本方案确定得当,在每一片FPGA芯片上可以实现四轴功能完全相同但彼此相互独立的操作,能够实现多轴联动,对于平面图形和三维图形处理,可以采用两轴和三轴联动即可。

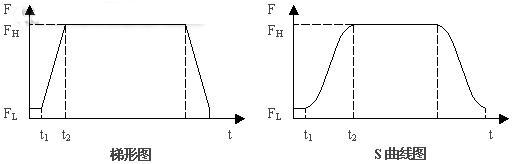

在高速往返运动和快速行推进过程中,如果不加技术处理,如梯形图所示,在加速度很大的高速运动过程中,就会出现振动、冲击,图形就会出现不规则的错位,严重时就会出现类似波纹状的变形。经过现场反复的实验,在同一设备上,可以大大的提高工作效率和图形的加工质量。

为了存储大量的扫描数据和达到同步扫描的目的,我们巧妙地利用了FPGA内置的2MBit块RAM资源来存储每行的图象数据。在本设计中,我们开辟了9根地址线寻址的32Bit数据总线接口的RAM区,即16KBit。如果每个扫描象素为0.1mm,按最高的扫描精度,则理论上扫描幅面可以达到1.6m。扫描从低位地址向高位地址,从每行的低位向高位依次进行。因为DSP每次向FPGA的RAM区写入一行图形数据512×32Bit,所以在对这些16KBit数据处理期间,DSP不需再向FPGA写数据。不仅大大提高了激光设备的工作效率,而且也保证了扫描的同步性,对于往复扫描出现的整体错位,在软件上进行反向补偿也提供了可行性。

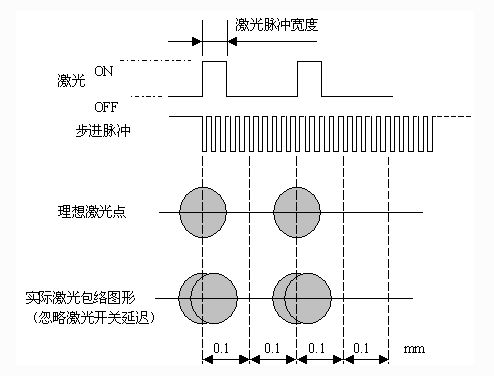

在同步扫描时,为了提高扫描精度,改善图像质量,我们增加了8位激光控制寄存器LCR,通过设置LCR的大小(0~255),来达到提高扫描精度的目的,请看如下分析:

位图像素控制激光开关存在的问题

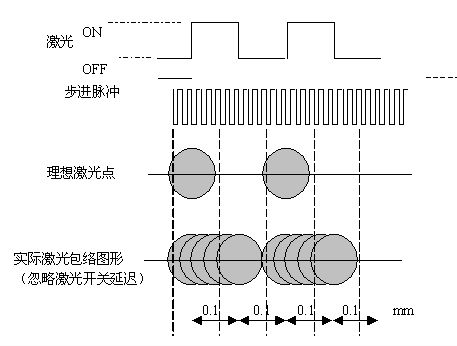

举例分析:假设位图数据为1010,光斑直径为Ф0.1mm,单像素脉冲数5,则步进脉冲和激光扫描如下:

从上面图形分析可以看出:如果完全根据位图像素控制,激光

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- Xilinx Virtex UltraScale 开发平台(06-12)