谁能缩短大容量FPGA的编译时间?增量式编译QIC!

按照相对论的理论,时间也是可以被拉长缩短的,只不过需要巨大的能量支撑着您达到一个和光速可比拟的高速度而已。这话说着轻松,你我心里都明白,估计咱们的有生之年是看不到这样的情景的……

回到可编程逻辑器件领域,随着65nm、40nm,乃至目前的28nm深亚微米工艺的采用,厂家生产出了越来越大,也越来越复杂的FPGA器件。而用户们在为FPGA不断增强的功能和不断下降的单位成本而欣喜不已的同时,也在为相关EDA软件的性能滞后所带来的开发效率相对降低而苦恼不已,尤其是对大容量FPGA芯片动辄10到20个小时的编译时间可谓怨气冲天。笔者在许多次面对一线的FPGA工程师时,都听到了这样类似的话:要是编译时间能压一压就好了!

Altera不能真的压缩时间,但我们能改变"速度"!从数年前的版本开始,Quartus2软件中就整合了一种新技术,或者说一种新的设计流程:增量式编译(Incremental Compilation)。它是ALTERA为解决大容量FPGA设计编译时间太长的问题给出的一个新式工具!您,了解它吗?

增量式编译原理及流程

增量式编译QIC的原理很容易理解:对一个复杂的设计而言,肯定是需要做一定的功能划分,由不同的子功能模块来实现。那么在设计进入后期比较成熟的时候,前后两次编译的设计版本中,会有很大部分的电路逻辑都是相同的(没有修改),如果能在后一次编译中,重复利用前一次编译中未改变部分的编译结果,也就是相应部分的布局布线信息,那么就能把这部分逻辑所消耗的布局布线时间节约下来,从而在很大程度上缩短整个设计的编译时间。当然,聪明的读者都能想到,这样的编译方式,除了能缩短编译时间,还能支持许多别的用途,比如IP设计交付、团队开发、不改变正常设计结果插入调试接口等。这些确实都是ALTERA 增量式编译能够实现的功能,但在本文中我们只阐述QIC在缩短编译时间方面的作用。

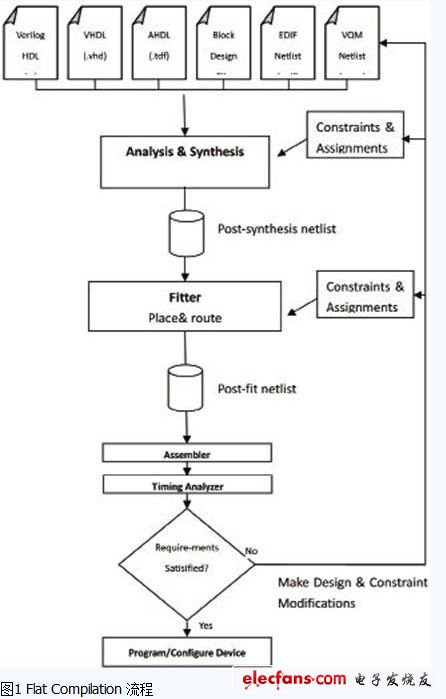

增量式编译原理虽然简单,但要在FPGA的EDA软件中实现,却是一个复杂的系统工程。它不是简单地在软件中增加一个功能模块,而是对编译处理流程多方面的改变和增强!请比较图1和图2两幅附图:图1是传统的FPGA编译流程(Altera名称:Flat compilation),图2则是增量式编译流程的示意图。我们很容易发现增量式编译流程复杂了许多,不仅引入了一些新的概念,比如设计分区(partition)、分区综合后网表、分区布局/布线后网表等,同时加入了新的处理阶段--分区合并(partition merging),而且对分析综合(Analysis&Synthesis)和布局布线(fitter)阶段进行了改进,增加了许多针对分区的具体操作。

经过几年的研究与实践,QuartusII的增量式编译已逐步完善,无论是在可操作性、稳健性方面,还是在缩短编译时间的效果方面,都十分出色。笔者参与的几个客户项目中,通过QIC的实施,都得到了50%左右的编译时间节约,极大提高了客户的开发效率。下面,我将结合这些实际项目中的经验,介绍如何实践利用QIC来高效的缩短设计编译时间。

QIC实践

QIC的效果评估

在讨论具体如何使用QIC之前,先考虑一个问题:如果读者在您的工作中使用了增量式编译QIC,怎么评估它的效能呢?

您需要至少做3轮实验,才能看到QIC节约编译时间的效果。首先,需要把您的设计用传统编译流程Flat Compilation进行编译,记录下各阶段所花费的时间。然后,创建合理的设计分区,指定分区网表性质,进行第二次编译,得到QIC各个分区的初始网表,并请记录下操作时间。第三次编译,您可以选择修改设计中的某一个分区,然后再编译一次,记录下操作花费的时间。将第三次的编译时间和第一次相比,正常的话应当看到非常明显的时间节约,这才是QIC增量式编译在编译时间节约方面的体现。

值得注意的是,第二次编译中已经使用了QIC,但往往花费时间和第一次编译差不多,有时还有增长。许多人为此怀疑QIC的性能,认为QIC没有效果甚至恶化了编译时间。这其实是一种误解!为什么呢?回到图2,我们可以看到,QIC流程在Analysis&Synthesis和fitter之间增加了一个新的处理阶段--分区合并,它是需要额外花费在第一次Flat Compilation中不存在的时间。而且,由于这是创建分区后的第一次编译,所有分区的网表都是空白的,也就是说整个设计都需要被编译、分析、综合、布局布线等的工作量和第一次编译是类似的,因此这部分花费的时间也是差不多。把这两部分时间加起来,自然第2次编译时间有可能会比第一次长了。只有当进行第3次编译的时候,各个分区都有可重用的网表了,才有可能

QUARTUS II EDA Altera FPGA 相关文章:

- 基于MC8051 IP核和FPGA的频率计设计(11-24)

- 基于FPGA和Quartus II的多功能数字钟设计与实现(11-18)

- FPGA核心知识详解(3):那些让FPGA初学者纠结的仿真(11-28)

- QUARTUS II中IP核的调用方法(图文详解)(02-16)

- 基于FPGA的ARM并行总线设计与仿真分析(07-15)

- 基于FPGA的数字密码锁(07-04)