谁能缩短大容量FPGA的编译时间?增量式编译QIC!

将那些没有设计改变的分区的网表重用,从而节约综合和布局布线阶段的时间,达到整体编译时间的节约。

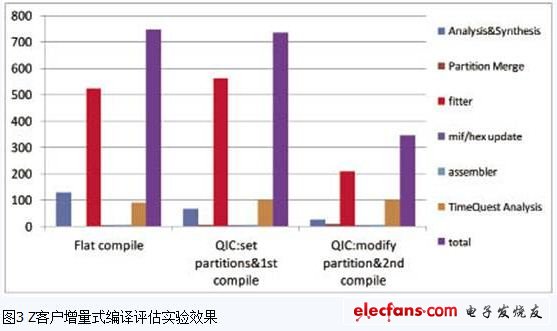

图3是笔者支持的一个客户所进行的QIC增量式编译性能评估的结果总结。客户的设计是高端路由器中的包处理应用,使用了ALTERA公司的Stratix4GX530器件,逻辑利用率大约是60%.客户的编译硬件是一台高性能服务器:

CPU:16core Intel(R) Xeon(R) CPU E7420 @2.13GHz

。 Memory:64GB

即使是如此,在不使用QIC的情况下,客户的每次编译都需要12到13个小时。而在使用QIC并根据QIC指导原则进行了必要的设计优化后,最好的实验结果是可以在6个小时左右(大约350分钟)完成一次编译,节约了接近55%的总编译时间!从图3中很容易看出前面文字描述的几个特点:

1. 第一次编译和第二次编译的总时间差不多(750 VS 730)

2. 第三次编译中,Analysis&Synthesis操作的时间,fitter操作得时间都比第一次编译有非常明显的降低;

3. 从原理上看,QIC的网表重用对Assembly和时序分析没有直接影响。因此三次编译中,Assembler和时序分析所花费的时间是差不多的。

QIC指导原则

合理创建分区

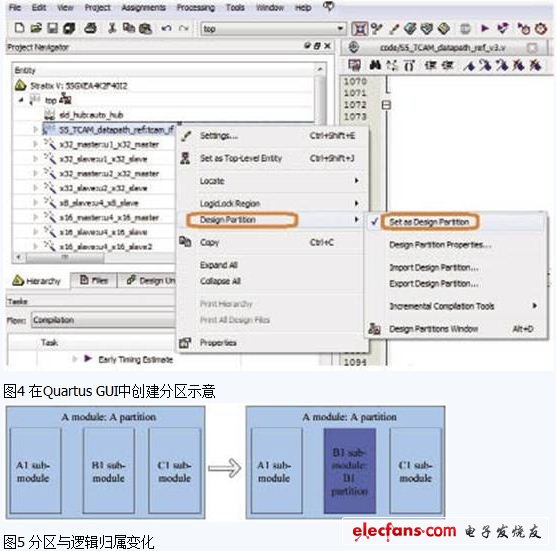

Quartus中的"分区"是和设计层次紧密关联的。任何设计,无论简单还是复杂,都会有一个顶层模块(top-level module),Quartus自动将它设置为一个默认分区(命名为top),不需要用户设定。而别的分区,需要用户手动创建。创建分区的方法很简单,在Quartus GUI界面左上角的Hierarchy窗口,选择想创建分区的实体,右键唤出的菜单中选择"Design Partition",然后在下一级菜单中选择"Setting as Design Partition",分区就创建成功了。

从图2可以看出,分区(Partition)是增量式编译中的一个关键概念。Altera规定:只要是有完整设计边界的设计实体,无论它在设计的哪一层次,都可以用它来创建设计分区。也就是说,Quartus II中,设计中任何层次中的任何一个设计模块,可以作为一个设计分区;一个设计中也可以包含不止一个设计分区;即使是在设计的同一层次,也可有多个分区。同时,请注意:分区之间没有层次关系,任何逻辑只能归属于某一个分区。以图5为例,A模块由A1、B1、C1三个子模块组成。如果A模块被设置为分区,Quartus会用模块名来为此分区命名:A分区。那么,A分区中就会包含A1、B1、C1三个子模块的所有逻辑。但如果把B1子模块也创建为分区,那么,A分区中就只包含A1、C1两个子模块的逻辑,B1子模块的逻辑只属于新的B1分区了。

从前面分区的性质和特点可以看出,对包含多个功能模块的多层次复杂设计,可以有许多种设置分区的方案。但需要注意的是:不是任何一种分区方案都能带来编译时间的节约,恶劣的设计分区甚至能够导致编译失败!如何得到高效合理的设计分区呢?我们需要遵从以下原则:

a. 不要创建太多的分区,一般性的设计建议分区的数量控制在4~8个之间;

b. 不要创建太小的分区,一般建议不要小于1000个LE或者ALM;

c. 外设接口逻辑和内核处理逻辑放到不同的设计分区;

d. 相同或相近功能的外设接口,如果管脚位置相邻,可以放在同一个分区,否则创建不同的设计分区;

e. 不同的分区方案中,分区之间的联接少的方案更优。

针对QIC优化代码

除了分区方案,设计代码也对QIC的性能有直接的影响,需要设计者针对QIC做一些特定的代码优化。优化主要有两方面,一方面是升级所使用的Megacore IP到最新的版本;另一方面则是一些更严格的编码规则。

之所以建议升级Megacore IP到最新的版本,这是由于QIC增量式编译常常需要调用Megacore IP的一些特性来支持一些特定操作,而这些特性通常在较新的版本中才能得到比较好的支持,而且随着QIC的成熟不断改进。笔者就曾经在一个尝试使用QIC的项目中,发现客户的设计继承了一部分老项目中的代码,其中包含好几个Quartus 9.1版本的DDR EMIF控制器,占了整个设计使用资源的20%左右。当说服客户把这几个控制器升级到当时最新的Quartus 11版本,发现QIC所能节约的编译时间增加了近1个小时,大约15%的整体编译时间。

之所以QIC要求遵从更严格的编码规则,这是由于Quartus在有分区存在的时候,是不对跨越分区边界的逻辑进行综合优化,一些在Flat compilation中可以被软件优化掉的不良代码,在QIC的流程中会造成严重的影响。这些严格的编码规则包括:

a. 不要在底层分区边界上使用三态信号和双向端口;

Altera器件中,只有在器件的输出管脚上才能实现真正的三态信号,在器件内部,

QUARTUS II EDA Altera FPGA 相关文章:

- 基于MC8051 IP核和FPGA的频率计设计(11-24)

- 基于FPGA和Quartus II的多功能数字钟设计与实现(11-18)

- FPGA核心知识详解(3):那些让FPGA初学者纠结的仿真(11-28)

- QUARTUS II中IP核的调用方法(图文详解)(02-16)

- 基于FPGA的ARM并行总线设计与仿真分析(07-15)

- 基于FPGA的数字密码锁(07-04)