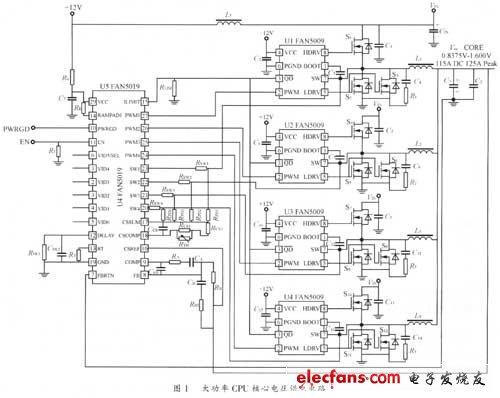

大功率CPU核心电压供电电路的设计

1 引言

当今的高速中央处理器(CPU)在提供极高的性能的同时,对于其供电电源的各项指标的要求也达到了前所未有的高度。更高速的CPU需要更低的核心电压,却需要更大的功率,因此供电电路必须提供极大的电流。更好的解决核心电压的供电问题已经成为电压变换模块和PC主板设计者面临的极大挑战。

2 Intel相关规范对CPU核心电压的要求

Intel早期的CPU,如Pentium 2、Pentium 3都遵循Intel的VRM(Voltage Regulation Module)8.1~8.4电源规范,其最大输出电流值为22.6A。Tualatin核心的Pcntium 3及Celeron CPU则开始引入VRM8.5标准,其最大输出电流值为28AIntel在推出Willamette、NorthWood核心的Pentium4时引入了VRM9.O标准,其规定的最大输出电流为70A。随着Prescott核心Pentium 4的推出,VRM规范也更新到了VRD(Voltage Regulator Down)10.O,电流最大值也达到了91A。为了配合更高频率更高性能的CPU,200 5年4月Intel推出了VRDl0.1规范,对LGA775 Socket的CPU的供电电源的规格指标进行了细致的规定,这是对台式机CPU供电电源要求极高的电源规范,其要求列举如下:

(1)连续负载电流(ICCTDC)为115A;

(2)最大输出电流(ICCMAX)为125A;

(3)输出的电压值由VID[5:0]指定,范围为O.837 5~1.6V.以0.0125V为步进;

(4)负载线斜率(loadline slope)阻抗R0为1.00mΩ;

(5)最大电压纹波VRIPPLE为±5mV;

(6)最大电压上冲波峰VOS_MAX为50mv,其最长持续时间为25μs。

这里只是列举了最为重要的几个规定,VRDl0.1规范还有其他的许多内容,限于篇幅,这罩不再一一列举。由上述内容可见,高性能CPU对于供电电源电路的输出功耗需求越来越大,在VRDl0.1中要求输出功耗甚至高达170W以上。同时对于电压的精确性和稳定性的要求也达到了非常苛刻的地步,在大功率、大电流的情况下还要保持非常稳定和精准的负载线斜率。在VRDl0.O之前,CPU核心电压供电电路一般都是由三相或两相的PWM控制方式,这种方式已经无法满足100A以上的大电流需求。本文的设计使用了4相PWM控制,可以满足VRDl0.1的严格要求,以下详细叙述之。

3 大功率CPU核心电压电路的设计

图l所示即为本文提出的满足VRD101要求的大功率CPU核心电压供电电路。它使用了仙童(Fairchild)公司的FAN50192—4相PWM电源控制器做为丰控制芯片。FAN5019控制4个Fairchild的FAN5009 MOSFET驱动器。FAN5009驱动开关外接的高端和低端M0SFET,然后通过电感与电容器件的充、放电对VCCCORE进行供电。

FAN5019是一款多相(最高支持4相)DC/DC控制器,专为产生高电流、低电压的CPU核心电压而设计。本设计中,它以并行的方式同时驱动四个PWM通道,而且以交叉开关的方式来减少输入、输出的纹波电流,这样可以达到减少外围器件,降低成本的目的。FAN5019采用了温度补偿电感器电流检测技术,来满足VRDl0.1规则的负载线技术要求,而一般的PWM控制器都是采用RDS(ON)或感应电阻器来测量电流和设置负载线,精度无法满足要求。如图1所示,FAN5019的VID[5:0]输入与VRDl0.l规范定义完全一致,可以控制输出0.8375~1.600V以12.5mV步进的电压,另外它还具有短路保护,电流上限可调,过压保护等增加安全可靠性的技术。FAN5019向每个FAN5009送出PWM控制信号,而FAN5009通过内部电路将其转换为可以正确驱动高端和低端M0SFET的信号输出。FAN5009可以同时驱动高端和低端的MOSFET,其内置启动二极管,因此无需在外围电路中再添加二极管。

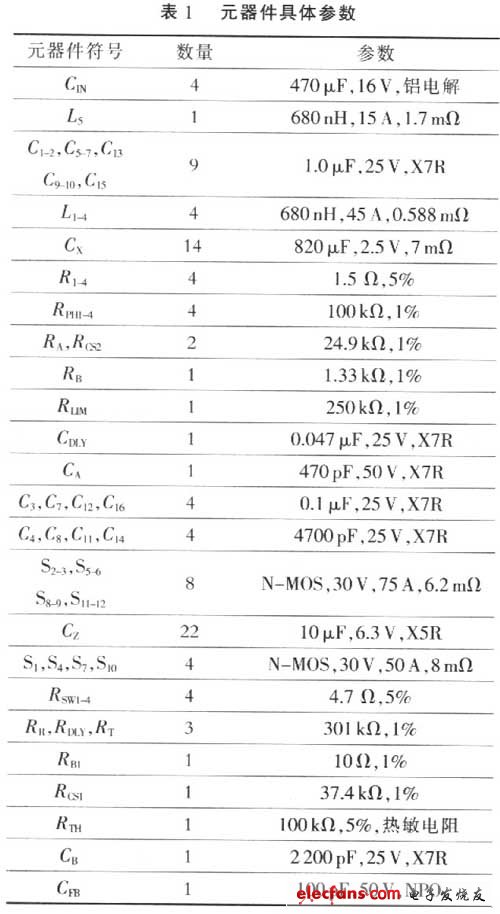

本设计的输入电压VIN为12V,额定输出电压VVID为1.500V,占空比D(Duty Cycle)为O.125,负载线斜率阻抗R0为1.OmΩ,ICCTDC大于115A,ICCMAX为125A,最大输出功耗为172.5W,最大电压纹波VRRIPLE为±5mV,每相的开关频率fSW设定为228kHz。外围元器什的具体参数如表l所列。

4 重要器件的选择与布局布线规则

4.1 功率MOSFET的选择

在选择高端和低端功率MOSFET时,主要考虑如下几个方面:

(1)较低的RDS(ON),应小于1OmΩ;

(2)尽可能高的导通电流;

(3)额定VDDS应该大于15V。

在选择低端MOSFET时,RDS(ON)是最重要的考虑因素,因为在正常工作时,低端的MOSFET导通时间较长,因而功率消耗较大。因此在本设计中.每相在低端都使用了两个FDD6682,其导通电流为75A,在VGS为10V时(正常工作状态),RDS(ON),为6.2mΩ,额定VDDS为30V。对高端的MOSFET而言,门电

- 基于自适应技术的CPU供电电路系统(10-27)

- 嵌入式CPU卡在医用便携式监护仪中的应用及设计(09-23)

- 四核Vs八核移动处理器 性能差异并不大(03-10)

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 评测:采用AMD APU平台的联想启天M5800——均衡+全能(02-17)

- 智能手机省电秘诀:看如何从设计源头来降低功耗(02-14)