揭开Altera公司支持OpenCL的设计工具的神秘面纱

将程序中处理负荷较大的工作分配给加速器LSI的"异构计算(Heterogeneous Computing)"将踏出崭新的一步。美国Altera公司将于2013年内开始面向普通用户提供可自动由按照异构计算标准规格"Open-CL"编写的程序生成FPGA专用电路的工具"Altera SDK forOpenCL"。

将微处理器(CPU)、图形处理器(GPU)及信号处理器(DSP)等结合在一起,并将这些处理器当做加速器使用的环境一直在不断完善。具体而言,半导体厂商主导成立的业界团体Khronos Group制定了OpenCL标准,GPU厂商美国英伟达提供了软件开发及运行环境"CUDA"。美国英特尔也于2012年11月发布了配备众核型处理器的加速器板卡"Xeon Phi"(开发代码名:KnightsCorner)的首款产品。按照用途使用不同架构处理器的异构计算正在稳步普及。SDK for OpenCL支持的FPGA板卡如下图,Nallatech公司的产品(上)和BitWare公司的产品(下)

由程序生成电路

Altera的SDK for OpenCL与传统工具的不同之处是,用户开发的程序并不是在固定架构处理器上运行的,而是由这些程序生成FPGA上的逻辑电路。在处理能力及功耗等方面,有望获得与制作专用硬件时接近的性能。

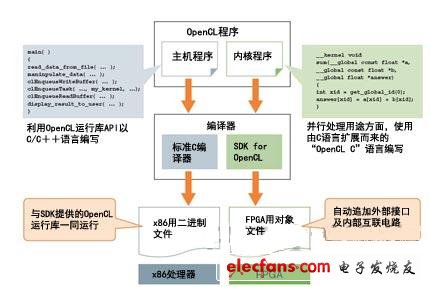

具体而言,可将按照OpenCL标准开发的程序中的加速器用程序(在OpenCL中称为"内核"程序)转换成FPGA上的逻辑电路,并将其作为FPGA的配置数据输出(图1)。运行时,主机端的程序会通过OpenCL用运行库,要求已被写入这些配置数据的FPGA进行内核处理。

该工具的最大优点是,程序员可在不具备硬件设计知识的情况下生成FPGA的配置数据。使用以前提供的开发工具,也能将以C语言编写的程序转换成FPGA上的逻辑电路。但是,要让逻辑电路完成数据处理工作,需要由CPU通过某些通信接口收发数据,而且为FPGA连接外部存储器的话,还必须设置存储器控制器等。因此,程序员需要具备可设计具备各种外围电路的系统LSI的知识。

图1 可自动由C语言程序生成FPGA内的电路

使用Altera"SDK for OpenCL"的设计流程。可将根据OpenCL的规定编写的外部设备用内核程序转换成FPGA上的逻辑电路。

追加固定的外围电路

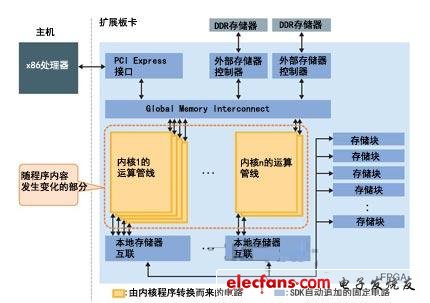

Altera采用的方法是未降低FPGA本身所具备的灵活性,而是提高了方便性。SDK for OpenCL可在由内核程序转换而来的逻辑电路上,自动追加用来与主机处理器通信的PCI Express接口、外部存储器控制器、内部互联等固定电路(图2)。由此,能够以最终形成系统LSI的形式输出配置数据。

图2 自动追加接口电路

只将内核程序转换成新的逻辑电路。关于用来和主机交换数据的接口电路、存储器互联电路等,均会自动追加固定电路。

但是这样做就无法修改电路,比如使用其他接口电路,或者采用不同的互联电路等。目前支持的FPGA板卡也十分有限。可以说这套系统优先考虑的是为软件开发者创造出可以使用FPGA的条件。

如果软件开发者预先按照OpenCL规格编好程序,就能轻松比较出"使用GPU还是FPGA作为加速器才能获得高性能"等。OpenCL消除异构计算中程序与硬件架构的依赖关系的目标正在不断实现。

Altera公司已向参加优先体验计划的数十家企业提供了SDK for OpenCL。目前支持的是主机处理器使用x86架构CPU、以PCI Express接口与Altera公司的FPGA通信的系统。

2013年面向普通用户提供时,Altera公司还计划使其支持集成有CPU内核"Cortex-A9"和外部接口等外围电路的"SoC FPGA"。SoC FPGA可利用Cortex-A9作为主机处理器,在FPGA区域构建加速器电路。其优点是,能够利用比PCI Express带宽大、延迟小的接口进行主机处理器和加速器电路之间的通信。

OpenCL PCIe Altera FPGA DSP 相关文章:

- 高性能汽车和FPGA:共同点比您想象得多(09-09)

- 什么是OpenCL?面向FPGA的OpenCL有何优点?(03-12)

- 基于OpenCL标准的FPGA设计(04-26)

- Mali GPU编程特性及二维浮点矩阵运算并行优化详解(07-07)

- 抢攻数据中心 赛灵思发布OpenCL开发工具(02-10)

- 基于PCIe的WarpDrive SLP-300加速卡(10-23)