详解FPGA开发流程中每一环节的物理含义和实现目标

。然后通过判断触发点来检查采集数据,一旦满足触发条件,这个时候会停止扫描,然后将触发点前后的一些数据返回给PC端的测试工具进行波形显示,供开发者进行调试。

目前的调试工具都是和本身的FPGA开发平台挂钩的,不同FPGA厂商都会有开发软件平台,嵌入式逻辑分析仪也就不同。Altera 厂家提供的是SignalTapII,而 Xilinx厂家提供的是 ChipScope,这些工具的具体使用在后面工具中详解。

当然这里除了嵌入式逻辑分析仪外,各厂家还提供了一些其他的在线调试工具,例如SignalProbe等等,但是或多或少的用的人不是很多,有兴趣的可以找到该功能使用的说明手册。

FPGA开发— 配置及固化

好了,到了我们最后一个环节就可以完成FPGA的流程了。这一部分我们分四个小节来讲,首先是针对大家很多人不是太清楚的FPGA配置过程安排的,随后一节为了更加深理解,举了altera 的FPGA叙述配置全过程,第三小节是探讨FPGA主要的配置模式,最后一节就是正对这些配置模式展开的对比选择探讨。

FPGA开发— 配置过程

在FPGA正常工作时,配置数据存储在SRAM中,这个SRAM单元也被称为配置存储器(configure RAM)。由于SRAM是易失性存储器,因此在FPGA上电之后,外部电路需要将配置数据重新载入到芯片内的配置RAM中。在芯片配置完成之后,内部的寄存器以及I/O管脚必须进行初始化(iniTIalization),等到初始化完成以后,芯片才会按照用户设计的功能正常工作,即进入用户模式。

FPGA上电以后首先进入配置模式(configuration),在最后一个配置数据载入到FPGA以后,进入初始化模式(initialization),在初始化完成后进入用户模式(user-mode)。在配置模式和初始化模式下,FPGA的用户I/O处于高阻态(或内部弱上拉状态),当进入用户模式下,用户I/O就按照用户设计的功能工作。

举例——altera FPGA配置全过程

一个器件完整的配置过程将经历复位、配置和初始化等3个过程。FPGA正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态管脚nSTATUS和CONFIG_DONE管脚也将输出为低。当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

在接收配置数据的过程中,配置数据由DATA管脚送入,而配置时钟信号由DCLK管脚送入,配置数据在DCLK的上升沿被锁存到FPGA中,当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。因此,CONF_DONE管脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该管脚。在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。当初始化完成以后,器件上漏极开始输出的INIT_DONE管脚被释放,同时被外部的上拉电阻拉高。这时,FPGA完全进入用户模式,所有的内部逻辑以及I/O都按照用户的设计运行,这时,那些FPGA配置过程中的I/O弱上拉将不复存在。不过,还有一些器件在用户模式下I/O也有可编程的弱上拉电阻。在完成配置以后,DCLK信号和DATA管脚不应该被浮空(floating),而应该被拉成固定电平,高或低都可以。

如果需要重新配置FPGA,就需要在外部将nCONFIG重新拉低一段时间,然后再拉高。当nCONFIG被拉低吼,nSTATUS和CONF_DONE也将随即被FPGA芯片拉低,配置RAM被清,所有I/O都变成三态。当nCONFIG和nSTATUS都变为高时,重新配置就开始了。

配置模式

这一块分成两部分,一部分是在线调试配置,另一块是固化,即将工程配置到相应存储单元中,上电后,通过存储在存储器中的内容配置FPGA。

在线配置

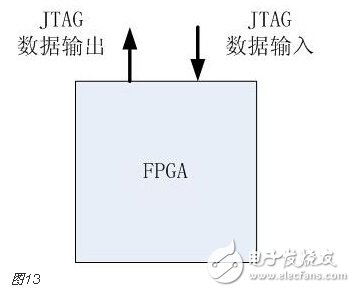

第一部分在线调试配置过程是通过JTAG模式完成的,如图13所示,在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

JTAG接口是一个业界标准接口,主要用于芯片测试等功能。FPGA基本上都可以支持JTAG命令来配置FPGA的方式,而且JTAG配置方式比其他任何方式优先级都高。JTAG接口有4个

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)