详解FPGA开发流程中每一环节的物理含义和实现目标

他输入方式的繁琐的输入的厌恶,更是爱的无法自拔。当开始强制性要求开始时养成多用HDL输入的习惯的时候,有些甚至有着痛心疾首般的痛苦,但是随着学习的深入,做的东西越来越大,尝到HDL输入方式带来的甜头的时候,就会觉得那个苦没有白吃。

我觉得原理图输入方式从现在的一些线索看来,在今后的某一天将会服役终结。首先是找到了原理图自身带有优势的替代品,那就是主流FPGA集成环境中的综合器和第三方综合器都具有RTL视图生成功能,这个视图完全展示了项目的结构组成,可以上下分层,最大的好处就是可以检查核实写的RTL级代码的综合后电路情况。还有一条线索是,大家用的仿真软件Modelsim并没有提供原理图输入的支持,是原理图的设计必须在集成环境成转换成RTL级代码或是综合成网表形式来做仿真,也是一件繁琐的事。原理图的离开只是时间问题。

至于目前HDL选择哪一种比较好,这个问题放到开始将HDL基础语法知识的地方进行探讨。这里要说明的是,并不是我们这里讲Verilog使用就否定其他的HDL语言。各种HDL的争端从未停止过,现在还是依然存在四种开发人,第一种是使用Verilog/System Verilog的人,第二种是使用VHDL的人,第三种就是使用System C的人,第四种是混合型的人,到底哪种好,也有也许是时间问题吧,时间证明一切。

综合

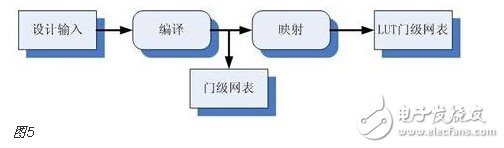

不管你是采用单一的输入方式,还是采用的是混合编程(这种在很多跨公司合作项目中会碰见,也许A公司用的是VHDL,B公司用的是Verilog,那这个项目中很大可能采用混合型),我们统称得到设计输入后,都得把设计输入得到一个可以和FPGA硬件资源相匹配的一个描述。假设FPGA是基于LUT结构的,那么我们就得到一个基于LUT结构门级网表。在这个过程中,又可以分为如图两个步骤。

需要说明的是在Altera的开发流程中,将编译、映射过程按照我们叙述的合称综合,而在Xilinx开发流程中,由设计输入得到门级网表的过程叫做综合,而映射过程归结到其叫做实现的某一子步骤中。但是整体的流程还是遵循这个顺序的,只是叫法一些外表性的不一样而已。

FPGA开发—编译

原理图、HDL、IP核这些都将通过编译后生成门级的网表,这里生成门级网表的过程其实是早起ASIC的步骤,直接生成门电路网表。这个时候的网表文件和具体的器件无关,也就是说,生成的门电路网表也是一种平台移植的媒质。

FPGA开发—映射

我们通过编译得到一张门级网表之后,与早先ASIC开发流程中在这个门级网表布线后去做掩膜不同,接下来就得考虑如何与我们选择的硬件平台结合起来,毕竟我们使用的硬件平台是由一个一个的LUT(假设这类FPGA)组成的。那么这个结合的过程就是映射过程。

这个过程其实很复杂,首先需要把形成的网表逻辑门给规划成一些小的组合,然后再去映射到LUT中,这个过程中规划按照一定的算法和章程进行。不同的算法和章程就会得到不同的映射,不同的映射就会为后面的过程提供不同的选择,最终生成性能不一样的电路了。

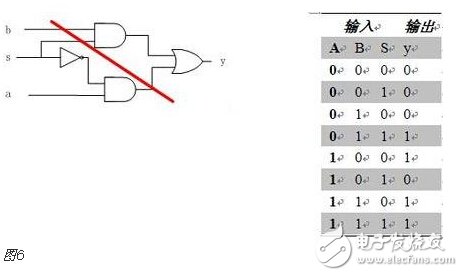

我们把讲基于SRAM技术的FPGA的二选一多路器拿出来举个例子,如图6,可以按照红色线将二选一多路器完全劈成两边,原来的一个表就可以规划到其他两个表或表内容中,因为被劈成的两部分可单独成表,也可以被规划到其他电路形成的表里。

映射的工程比较复杂,运算量也很大,也是为什么FPGA开发过程中,一直存在的一个问题,形成最终的可配置二进制文件的时间非常长,特别是一些大一点的项目,时间消耗比较长的一个点就是映射了,至于具体的映射算法就超出了书的范围了。再强调的是,映射是和器件有关的,即使是同一个系列,不同型号的FPGA内部就够也是有区别的,好比从外观看都是一个单元楼内的单元房,但是每个单元房内装修、家具摆设等都是不一样的。

布局布线

FPGA开发—布局

讲到这一块,正好有这么一个例子来讲解这个概念。近来报道朝鲜希望在俄罗斯远东地区租用数十万公顷的土地用来培育农产品。咱先撇开今后的购买的成功与否,假设成功了,并且有了这个详细的希望培育的农作物的品种及数量,有各式各样的蔬菜、主粮、禽类畜养场、果树等等。我们前面做的那些流程得到的LUT门级网表就好比这样的清单。

得到这样的清单之后,我们再假设在这十万公顷的土地上,阳光、水资源、温差都有一定的分布。大家知道农作物的的成长和高量产或者与阳关有关,或者与水资源有关,或者与温差有关,并且禽类的畜养材料与农作物的副产有关。所以接下来要做的事情就是根据现有的自然条件和农产品的所需环境特点合理布

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)