详解FPGA开发流程中每一环节的物理含义和实现目标

局,哪些地适合做什么。

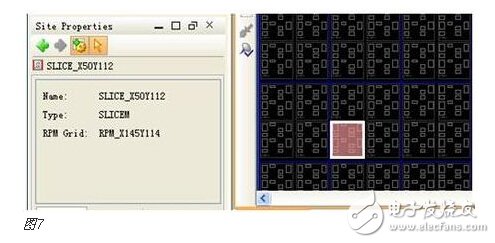

紧接着我们回到FPGA开发中来,我们通过前面的步骤得到的清单就是LUT门级网表。网表里提供的仅仅是从逻辑关系上一些LUT结构的连接。我们需要将这些LUT结构配置到FPGA具体的哪个位置。需要说明的是,FPGA里任何硬件结构都是按照横纵坐标进行标定的,图中选中的是一个SLICE,SLICE里面存放着表和其他结构,它的位置在X50Y112上。不同的资源的坐标不一样,但是坐标的零点是公用的。

在FPGA里布局需要考虑的问题是,如何将这些已有的逻辑上连接的LUT及其它元素合理的放到现有的FPGA里,达到功能要求的时候保证质量。具体点就比如,乘法器这样的电路适合放在RAM附近,当然,硬件乘法器的硬件布局一般也是在存储器附近,有利于缩短乘法的延时时间,什么样的电路需要配置高速等等。

十万公顷的地布局规划好了,农产品就会有很好的丰收,同样FPGA开发布局布好了,由FPGA搭建起来的电路就会更加稳定和扩展性。

FPGA开发—布线

上小节中,我们把十万公顷的地给安排好了,哪些地该种什么。具体实施之前还有一些是必须做的,比如农作物的浇灌,没有一个很好的灌溉系统是一个问题;再比如丰收了得采摘吧,这个时候,能够让大卡车到达每一块农地的公路枢纽也是需要解决的问题。将每一块或者相关的田地连接的灌水系统和公路的建设,就好比我们这个布线的过程。

我们在FPGA内通过布局,知道那些LUT具体分布到哪个SLICE,但是一方面如何让这些SLICE连接起来,二方面如何让输入的信号到达相应的开始处理点和如何让输出到达输出IO上,并且连接的电路整体性能好,这就是布线这个环节需要完成的内容。要达到布线最优话,当然这里面设计到布线算法和很多细节问题,比如涉及到布线资源、PLL资源分布。但是这些对我们理解布线这个概念没有很多益处,暂且不深入,本质上就是一个线路求最优的问题。

FPGA开发—约束

约束,在图1上看到,在综合和布局布线这两个流程环节里都出现了,我们暂且规定其为约束一和约束二,或者说综合约束和布局布线约束,布局布线约束又可以分为位置约束、时序约束。约束,就是对这些环节操作定制规则。一般开发环境会对这些约束有个默认,这些默认的设置对大部分情况下还是适用的,但是通常布局布线约束中的I/O约束是我们每一个工程都必须给定的。同时开发工具开放其他约束接口,允许我们设置这些规则,具体的有哪些约束怎么去做在后面介绍工具使用的时候进行讨论,这里先明白这些约束的基本概念。

FPGA开发—综合约束

相信大家已经下意识的将综合约束和综合过程挂在一起了,没错,综合约束确实是在综合过程中做的,用来指导综合过程,包括编译和映射。我们已经知道综合过程是将RTL级电路描述转换到FPGA上的硬件单元(LUT)中,形成以FPGA存在的硬件单元构成的电路。

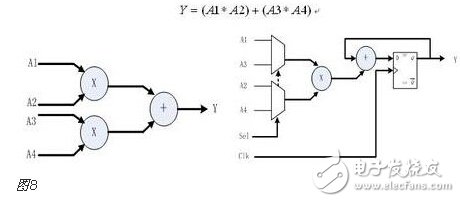

我们还是拿前面有过的例子来说明,不同的约束将导致生成性能不同的电路。综合这么一个完成式***能的电路,没有加资源共享得到的电路如图8左边所示的电路,而加了资源共享的约束后,得到的电路结构如图8右边的电路。

通过之前的分析,得到左边的电路结构资源消耗多但是速度快,而右边的结构消耗资源少,但是速度慢,乘法器需要分时复用。

当然这只是一个例子,但是足以说明,不同的综合指导原则也就是综合约束,将会产生不同的电路。当得到的电路性能不能满足需求的时候,适当考虑综合约束,来达到一个速度和面积的转换的效果,实现性能的提升。电路实现的速度和消耗的面积是贯穿在FPGA开发过程中两个 矛盾的问题,综合约束是其中一种小范围内实现速度和面见平衡点移动的方式。

FPGA开发—位置约束

没错,你又想对了,位置约束和我们布局有关系,它就是指布局的策略。根据所选择的FPGA平台现有硬件资源分布来决定我们布局。

其中最典型的位置约束就是I/O约束。一个典型的系统是既有输入也有输出的,而不管是输入还是输出,都是从I/O上为端点的。输入从哪个端点进来,输出从哪个端点出去,输入是需要支持什么样的电气特性的端点,输出又是需要支持什么样的电气特定的端点。这些都是I/O约束做的事情。任何一个工程,都必须有这么一个约束。

还有一种典型的位置约束是在增量编译里涉及的物理界定。增量编译的出现就是因为在FPGA开发过程中综合和布局布线的长耗时性而提出的。思想就是把FPGA切成很多个小块的FPGA,然后约定具体哪块小FPGA放置什么模块,实现什么样的功能,从物理上进行界定。当修改工程后,开发平台就会检

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)