详解FPGA开发流程中每一环节的物理含义和实现目标

测哪些小FPGA内没有进行修改,哪些进行了修改,然后将修改过的部分重新进行综合布局布线步骤。这样一来,相比原来修改一点,全工程重新经过那些过程来讲,时间节省下来了。

FPGA开发—时序约束

估计没有多少悬念了,时序约束很大程度上和布线有关。为什么要做这个约束?

由于一方面信号在芯片内传递是需要消耗时间的,另一方面大量存在的寄存器有反应时间,而我们开发的最开始的时候这些时间都是理想化的。但是考虑到真实情况下,如果跑的速度比较高,达到了200M这么个速度,当然这个高速和具体的芯片有关,高性能的芯片本身跑的速度可以达到很高,200M相对来说就不是高速,对一些低性能芯片还可能达不到200M。这个时候,这些时间达到了同样一个系统时间数量级的时候,很可能影响电路的性能了。某一刻,该来的信号没有来,默认的话就会采集错误信号了。

为了让这些硬件本身带来的延时时间更理想化,我们就要对这些决定时间延时的因素优化来减少时间延时。对于寄存器本身的反应时间这个因素我们开发者是无能为力的,我们要做的优化就是布线了。是走直线还是走其他,不仅仅决定于自身这条路径,还和整个系统布线有关,好比水桶原理,系统性能决定于最差路径延时。

时序约束做的就是这些事情,但是时序约束并不是指具体去连接每一条线,这个工作就像前面那些流程一样都是由软件去实现的,先用软件自己默认原则布线,然后对其结果分析,不满足时序要求的,我们再对具体的问题路径做一些指导约束。时序约束的添加,主要包括周期约束、输入偏移约束和输出偏移约束。具体的过程在后面章节介绍工具使用时会有具体动手的指导。

FPGA开发—仿真

在经过上面从设计输入到综合再到布局布线过程的介绍后,我们来集中探讨一下,在这些过程中涉及到的相应的仿真。

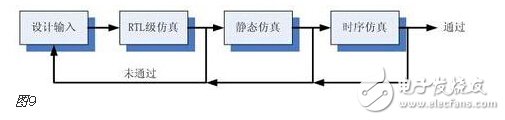

仿真,字面上讲就是模拟真实状况。我们FPGA设计里面的仿真,就是模拟真实电路的状况,查看电路是不是我们需要的电路。如果我们把FPGA开发形成电路当作一个产品的生产过程,那么在FPGA开发流程中含有的三种仿真(RTL级仿真、静态仿真和时序仿真)就好比产品线中的三道检测站。如图9,这三道工序任何一道出了问题,修改设计后都得重新走这三道卡,所以尽量在把问题发现在源头。

FPGA开发—测试平台

所谓testbench,即测试平台,详细的说就是给待验证的设计添加激励,同时观察输出响应是否符合设计要求。测试平台,测试平台在做功能仿真、静态仿真和时序仿真的时候都需要用到。刚开始的对于一些初学者,遇到的都是一些简单的东西,测试平台相应的也很简单,用一个文件就可以很清晰的呈现测试结构。对于一些复杂的项目,测试就没有那么简单了,由此还专门产生一个行业——测试行业。这个时候我们要用到一个概念就是结构化测试。

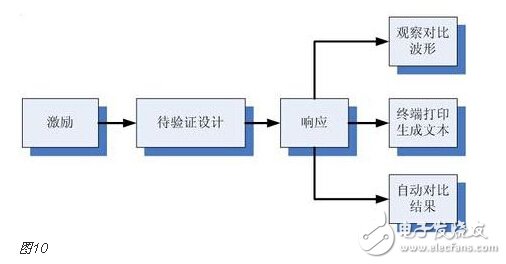

一个完整的测试平台如下图10所示,它是分结构组成的,其中对设计测试结果的判断不仅可以通过观察对比波形得到,而且可以灵活使用脚本命令将有用的输出信息打印到终端或者产生文本进行观察,也可以写一段代码让它们自动比较输出结果。

测试平台的设计是多种多样,可以使用灵活的Verilog的验证脚本,但是它也是基于硬件语言但是又服务于软件测试的语言,有时并行有时顺序,只有掌握这些关键点,才能很好服务测试。需要说明的一点是,不管大家是已经在用Verilog在写测试平台还是刚学习写测试平台,那么建议大家还是能用到System Verilog中相对Verilog新的语法还是尝试的用,System Verilog是一种趋势,它本身就是向下兼容的第三代的Verilog。

FPGA开发— RTL级仿真

这里RTL级仿真属于第一道检测,有些场合称作功能仿真,为了突出和后面的静态仿真的区别,以免在后面介绍静态仿真的时候大家弄的很头大,我们还是这样称呼。它是对工程在寄存器转送级进行的描述时进行测试,查看其在RTL级描述的时候实现的功能的正确性。

关于RTL级仿真,如果设计中设计到原理图输入的话,在一些仿真工具中是不支持的,比如Modelsim,这个时候要进行功能上的验证,可以将原理图转换成HDL描述,或者直接把整个工程转换成LUT门级网表后进行后面要讲到的静态仿真完成。

所有逻辑功能的验证都希望在RTL级做,尽可能的将问题发现在RTL级仿真过程中,减少后面发现问题带来的反复。

FPGA开发— 静态仿真

静态仿真,有些地方给的外号叫门级仿真,确切的说应该是综合后的LUT门级网表。是在综合过程后做的仿真。有些开发平台下将静态仿真具体又分为编译

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)