详解FPGA开发流程中每一环节的物理含义和实现目标

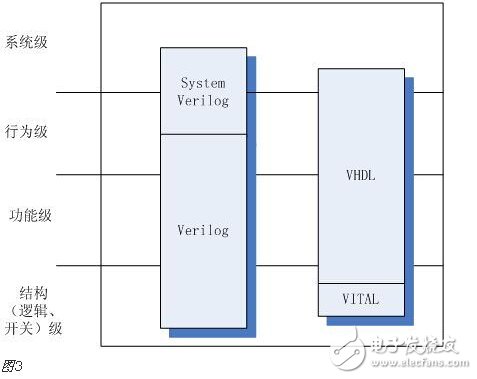

有开关级、逻辑门级、RTL级、行为级和系统级,如图3。其中开关级、逻辑门级又叫结构级,直接反映的是结构上的特性,大量的使用原语调用,很类似最开始原理图转成门级网表。RTL级又可称为功能级。

HDL语言除了前面提到的两种外,历史上也出现了其他的HDL语言,有ABEL、AHDL、硬件C语言(System C语言、Handle-C)、System verilog等。其中ABEL和AHDL算是早期的语言,因为相比前面两种语言来讲,或多或少都有些致命的缺陷而在小范围内使用或者直接淘汰掉了。而因为VHDL和Verilog在仿真方面具有仿真时间长的缺陷,System verilog和硬件C语言产生了,从图3看,System Verilog是在系统级和行为级上为Verilog做补充,同时硬件C语言产生的原因还有就是有种想把软件和硬件设计整合到一个平台下的思想。

FPGA开发—IP(Intellectual Property)核

什么是IP核?任何实现一定功能的模块叫做IP(Intellectual Property)。这里把IP核作为一种输入方式单独列出来,主要考虑到完全用IP核确实是可以形成一个项目。它的产生可以说是这样的一个逆过程。

在随着数字电路的规模不断扩大的时候,面对一个超级大的工程,工程师们可能是达到一种共识,将这规模巨大而且复杂的设计经常用到的具有一定通用性的功能给独立出来,可以用来其他设计。当下一次设计的时候,发现这些组装好的具有一定功能的模块确实挺好用的,于是越来越多的这种具有一定功能的模块被提取出来,甚至工程师之间用来交换,慢慢大家注意到它的知识产权,于是一种叫做IP知识产权的东西出来了,于是集成电路一个全新领域(IP设计)产生了。

IP按照来源的不同可以分为三类,第一种是来自前一个设计的内部创建模块,第二种是FPGA厂家,第三种就是来自IP厂商;后面两种是我们关注的,这是我们进行零开发时考虑的现有资源问题,先撇开成本问题,IP方式的开发对项目周期非常有益的,这也是在FPGA应用领域章节陈列相关FPGA厂家IP资源的原因。

FPGA厂家和IP厂商可以在FPGA开发的不同时期提供给我们的IP。我们暂且知道他们分别是未加密的RTL级IP、加密的RTL级IP、未经布局布线的网表级IP、布局布线后的网表级IP。他们的含义在后面陆续介绍FPGA的开发步骤的时候,相信大家能够恍然大悟。需要说明的是,越是FPGA靠前端步骤的时候提供的IP,他的二次开发性就越好,但是它的性能可能是个反的过程,同时也越贵,毕竟任何一个提供者也不想将自己的源码程序提供给他者,但是为了不让客户走向其他商家,只能提高价卖了,同时加上一些法律上的协议保护。那么越朝FPGA开发步骤的后端,情况就相反了,越是后端,IP核就会进一步做优化,性能就越好,但是一些客户不要的功能就不好去了。

FPGA厂商提供一般常用的IP核,毕竟为了让大家用他们家的芯片,但是一些特殊需要的IP核还是需要付费的。当然这里需要说明的是FPGA厂商的IP是很少可以交叉用的,这一点很容易想,对厂家来讲不会做这种给竞争者提供服务事情的。IP厂商一般会高价的提供未加密的RTL级源码,有时FPGA厂商为了扩大芯片市场占有率,会购买第三方的IP做进一步的处理后免费提给该FPGA芯片使用者的。

FPGA开发—输入方式使用探讨

在上面我们介绍了三种输入方式,有些地方会讲到第四种输入方式,就是门级网表文件输入的形式,我们这里并没有把它归为一种输入方式,原因在于,本身这些门级网表文件的产生还是源于介绍的三种输入方式中的一种或是几种混合的方式。所以这里没有把它归为一类。

好了,在上面三种输入方式介绍的基础上,我们来探讨一下这令人眼花缭乱的输入方式,探讨的目的就是为了让我们更好的使用他们。

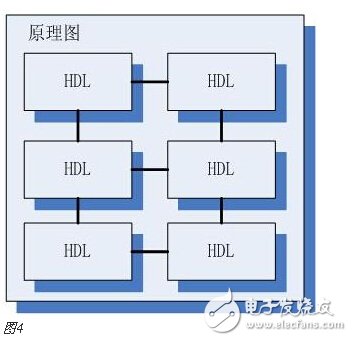

首先,来总结一下三者的优缺点,其实是两种,因为IP核不管是哪个层次,或者在原理图中被以符号的形式被例化,或者在HDL中被模块例化。所以这里集中探讨的是原理图和HDL的优缺点。原理图的优点就是结构直观性,HDL的优点是严密性、支持甚宽的抽象描述层次、易于移植、方便仿真调试等等,缺点就是不具备对方的优点。当时出现HDL的时候,人们确实是想着原理图该退出历史舞台了,但是到现在它还依然存在着。存在即是有道理的,存在就得用它,但是又得使用HDL,于是存在一种混合编程的形式。除了顶层模块用原理图之外,其他的内部子模块全部使用HDL来描述,HDL描述的模块可以通过工具转换成符号,然后在顶层模块中引用这些符号,这就完成混合编程。

在接触的很多FPGA的初学者很容易被原理图的输入方式给迷惑,甚至爱的深沉,加上本身其

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)