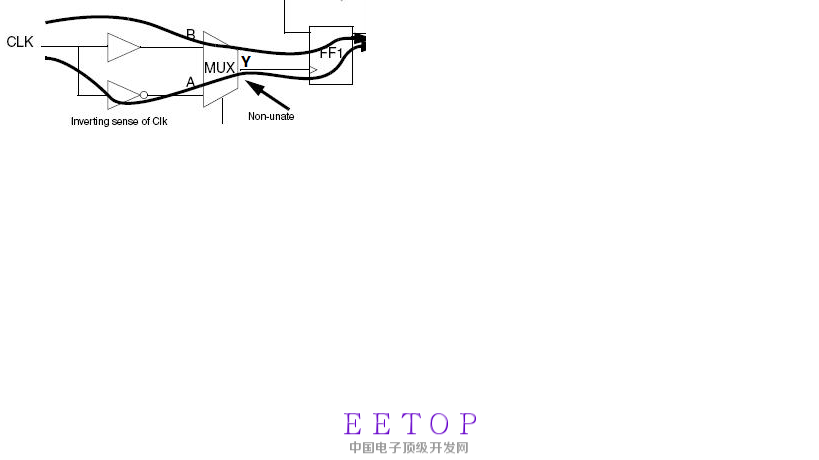

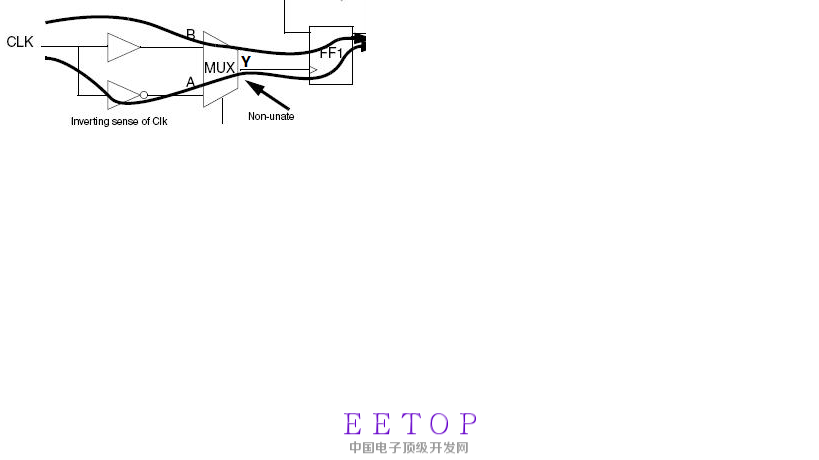

带invert 的mux时钟约束

时间:10-02

整理:3721RD

点击:

求帮助: 为啥mux输出时钟只有一条有时序检查,而反向输出时钟没有报出时序检查

create_clcok CLK

create_generate_clock clk_pos MUX/Y

create_generate_clock clk_neg MUX/Y -add -invert

create_clcok CLK

create_generate_clock clk_pos MUX/Y

create_generate_clock clk_neg MUX/Y -add -invert

设置了timing_enable_multiple_clock_per_reg true

还讲 clk_pos 和clk_neg 设置了 logically_exclusive

有人吗

使能端不会是接 tiehi/low 了吧

没有,使能端不是constant

不能设置logically exclusive吧? 设了就是说这两个路径只能存在一个了?

先create_clcok CLK,再create_generate_clock CLK_N,定义在反向器的输出端。这样两个时钟都能穿过MUX

你这个generated clock 定义的也太简单了点。

如果在MUX/Y 定义,那就把source 加上,两个gclock source 分别是mux i0 i1 。 -invtert option (icc 和 pt)可以去掉。

我这是简写的,应该不是这个问题吧

你可以把全的发出来,本身就是clock 定义引起的