请教一个clock的约束问题

时间:10-02

整理:3721RD

点击:

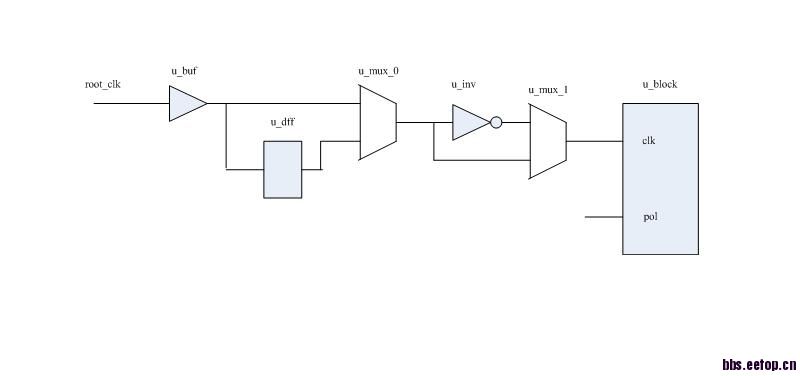

如图所示,要约束一个IP模块的timing,从图上看,有两个mux,那么一共有四个可能的clock

-divided_by 1

-divided_by 2 (reg那一路)

-divided_by 1 -invert

-waveform {2 3 4}

如果想要timing全面,是否这四个设置都应该用-add 加上去?

另外,block本身有一个端口控制内部采样沿,

如果想要check 正反沿采样的timing是否都满足,应该怎么设置?把所有的时钟waveform的可能性都描述出来?然后-add,

麻烦大家指点

最简单的方法是选一个最critical的clock path,条件是其他三个clock不会和第4个一起使用,或者有timing关系。

如果没有那么简单,就要依照具体情况分析了

最坏情况就是你说的那样

谢谢老大,应该都是exclusive的clock。

看来还是需要人工干预去减少一些场景的,不然一个设计中如果都是这样穷举clock的场景,会很没有效率吧