陈版主请教如果约束interface timing

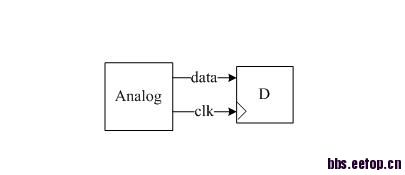

请问,如上图所示的analog和digital interface..请问该怎么设约束从而保证在P&R以后,我的data和clock仍旧保证一定的关系。不发生timing violation

多谢

设个输入clock吧,对数字部分, set_input_delay/output_delay设严格些,

保证余量可以 check setup,hold timing,

模拟部分不太清楚怎么约束

谢谢小编回复.现在analog里面不用管,就认为是从analog里面出来的clock和data是没有timing问题的.只要管从analog boundary到digital第一级flop之间的timing.

我的想法是要在保证在CTS以后,clock到达第一级flop的时间和data到达第一级flop的时间仍旧维持一定的关系,比如data比clock早到300ps..这样的情况该怎么设置约束..这个clock我已经设了.set_input_delay是设到data pin还是clock pin呢?set_input_delay具体是指什么样的delay? 这个具体的数值该怎么确定呢?

问下: 你这个都是analog 到digital的 input么, digital 没有到analog的output是吧?

set_input_delay 是设在digital的input port上,指的是外面用了多少,里面就剩下 一个clock period - input delay,

clock 自然也是从input port进去的,

这个不管,你可以这样, report_timing -from [some_input_ports ]-delay max/min ,

看看slack值是多少,这样就知道 最后有没有 setup,hold violation了,

clock定义在port上,

这个可以显示整个timingpath的路径, 你可以模拟analog部分的delay,

包括clock path

如果你的设计可以从analog和digital之间切开,就是说暂时不把analog作为你设计的一部分的话,

解决方法就是icfb说的set_input_delay的问题

首先你要知道从analog出来的clock和data的时序关系,就是它们之间最坏时相差多少,最好时相差多少,这个就是set_input_delay -max和-min的数值,剩下的事情,APR可以帮你去做

如果analog一定要成为你设计的一部分,那么analog和digital之间的连接就不是design的port了,也就无法用set_input_delay来约束那里的时序了。这时你就需要一个包含有同样信息的analog lib文件。如何生成这个lib文件是件比较复杂的事情

估计是ETM 吧, 或者ilm,

多谢两位小编的回复.

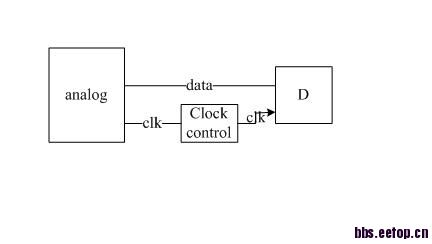

现在analog是当作一个blackbox..在我top level netlist只定义了input, outputs.所以可以不用管.所以应该就是小编说的set_input_delay要算准就对可以了.但我现在的结构就是clk从analog出来以后会先进一个clock control的module,这个module里面也有DFF,这样的话,APR tool也可以处理吗.在DC的时候我设时钟是设在clk control module的output上的.并不是设在source,PR的话应该会从source开始balance吧?

另外有个问题就是analog到digital之间的并不非得一个cycle 跑完..也可以是multi-cycle path...这个情况的话,怎么设multicycle path?from应该是从哪里开始?是从analog的data output吗?

另外,如果是从digital 到analog的话,是不是也同样子设output delay..这个值的话,是不是就是根据analog里面clk和data最差和最好的时相关系,从而再通过我想要这条path是个多少个cycle的path.这两个值一减得出来的啊?

谢谢

1) clock要设在source上

2) multicycle不一定非要-from

3) analog里面clk和data最差和最好的时相关系就是你要的output_delay,如果要multicycle的话,再设定

小编你好.因为我们公司以前做项目的flow都是在DC的时候,clock都设在clk module的output上.因为source上的同一个clock在不同的mode下面会有不同的频率..然后很多chip内部的很多module只工作在某一种频率下面..所以通过clock module出来的clock都是只供给那个特定的module用.因为我现在source clock只有一个,但通过clock module出来的clock会有很多组...请问这样会有什么问题吗?我每个clock module的结构都是完全一样的,就是为了给APRtools做CTS的时候能够比较容易的从source开始balance.

.只有在pt的时候,才会在source上设clock进行check..

create_clock at source clock

create_generated_clock at output ports of clock module

谢谢小编回复.那如果我这样子没有在source create clock.而还是create在clock module的output会如何?因为这个clock moudle并不是像clock divider一类的逻辑,只是做clock selection和enable作用.

我们公司以前的flow都是,clock module不参与综合,设置了dont_touch.已经自己手写了netlist,到时候会再放进去.每个clock module都完全一样,都是mux加flop的结构.为了保证逻辑一样..

可以吧 clock module放到数字模块一起 综合,考虑时序啊, 就看成是放大的digital部分啊,

省的烦,

难道这个clockgen 是独立在模拟和数字模块之间的另外的模块么,

DC综合时可以从clock module的output定义create clock,

但是在APR时,按照你#1贴说的要求,应该从source clock定义create clock,

除非你要求后端手动摆放所有clock module的instance,并且明确告诉他们你的时序要求。个人认为那样做的话,你是同时给自己和后端增加不必要的负担。结论就是,你的方法不是不行,但不是最好的。

谢谢回复.因为我在我原公司以前的做法都是clock module不综合.都自己手写netlist,这样保证用的cell一样,然后里面的timing也可能让所有的clock module都一样.所以这个时候的clock都设在clock module的output上. 最主要的问题是我们同一个source clk会有七八种频率.然后某些module只工作在某一频率下.如果从source设最快的clock freq.很多module都被over constraint了..而且我们也不喜欢在综合的时候设set case.所以才一个source clk经过clock module分出几十甚至上百个clock..从这里开始create clock.

谢谢陈小编回复.我在DC的时候这么设clock主要原因就是刚刚我回复icfb的.

我现在这个样子的话是不是就只能按照你说的,先让后端balance从source clk到clk module的output的这段delay...然后再开始从clk module的output开始balance到芯片内部其他的flop间的delay吗?

那我如果这样子做了.还是继续按照你之间和我讲的方法设set_input_delay 吗?谢谢.

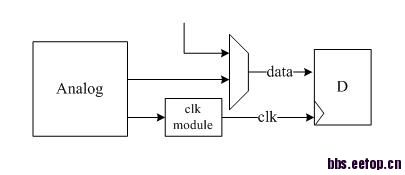

陈小编还有个问题要问一下,我这个input delay是按照如下的设法吗

set_input_delay -clock clk -max [get_pins data ]

如上图所示,那个mux还有一路输入是从另一个clk domain来,loopback mode.那个mode下面并没有input delay.

还有个问题,如果analog里出data和clk的时差差有可能是正,有可能是负,该怎么设max和min?

谢谢

你可以 source端 create_clock-name master_clock-period10[get_pinsmaster_source_pin]

然后在output 端 create_generated_clock -source[get_pins master_source_pin] -divide_by 4-name div4_clock [get_pins \

XXXoutput pin ]

每个generated clock都可以用 -divide_by , -multiple_by声明和master clock的关系啊,

这样比较清楚,你们综合的时候也不用手动例化, dont touch,

如何balance source clock和generated clock 完全是后端的工作, cts的时候可以balance各个 分频时钟,

其实也就是clockgen模块会有些clk buffer的调整变化,

问一个: 你source clock还去DATA模块么 ,还有leaf cell么,如果没有,那source clock的意义不大了,

完全是generated clock在起作用,

balance是你理解的这样,

balance clock和对数字port设 input,output delay是2码事情,

balance clocks只是为了各个clock domain的 之间的时序关系好,

input、output delay还是要设的, 是约束数字模块的DATA端的,

对,哦,没错,你就把数字当做大触发器好了, 就是check data和clk之间的边沿关系,

max、min应该可以模拟 你那个模拟和数字之间的关系吧, input /output delay ,

max/min说的就是2个极端情况,分别检查setup/hold timing, 你可以考虑2个极端情况,

比如正负的差值,

谢谢.source不去任何data,只去clock module经过一堆control,gating 而已.clock module的output才是去内部flop驱动data的..所以确实像你说的那样,只有generated clock 在起作用.

我的source clk关键是有七种频率,如果直接create在source的话,肯定只能create最快的一种频率吧..

比如我的source clk,可以是600MH\s, 500,300,100四种频率,然后芯片内部,A,B,C module跑在600,D跑在500,..E跑在100..这样子我通过clock module可以直接定义给各个module用的clock啊.

如果像小编你说的那样直接定义在source,再设generated clock,是不是就不太好处理这种关系呢,因为并不是divided_by或者multiply_by的关系啊..

恩.我也知道balance clock只是保证同一个clock到不同的flop之间的skew尽量小,然后或者不同的clock之间如果有skew要求的话,也要保证.

我现在主要是要保证,当clock和data从analog boundary出来以后,到我的第一级flop的时候,需要保证满足hold和setup.所以我觉得才要加约束,不然PR后,很有可能会有timing问题..

小编还有个问题..像我16楼帖的那张图..我发现我现在的timing report里面.有这么一条path,start point就是从我这第一级的flop开始,end point就是后面的flop,

这些flop都是neg edge trigger的,为什么timing report里面这个start point没有specify edge呢,而且工具反而认为是从pos edge开始的..?这样子我一看这条path就变成了只有半个cycle了..这是我约束里面哪里没有设对吗?

我是这样设clock的.

create_clock -name .. -period a -waveform { a/2, a}. ...

谢谢

那就没必要create 那个source clock ,create master/generated clock主要是为了描述

clock 分频倍频关系 和 balance 各个clock group,

你如果不是明显的 分频倍频关系 那就直接定义在clkgen module输出port上吧,不需要source clock了,

只不过要计算source到各个output port的延时,最好balance,因为你这些group直接是

有timing关系的吧,

没错.我现在就是让PR先balance从source到clk module的output这一段.设为第一级sync point,然后第二级的balance再从这些output开始到里面的flop..

小编可以再帮我看看我22楼问的问题吗.谢谢