基于网络编码的多信源组播通信系统,包括源代码,原理图等

| I/O | 信号描述 | ||

| decoder_in_rdy | 1 | O | 写SRAM控制器允许信号 |

| decoder_in_wr | 1 | I | 输入有效 |

| decoder_in_data | 64 | I | 输入至SRAM控制器数据总线 |

| decoder_in_ctrl | 8 | I | 输入至SRAM控制器控制总线 |

| reset_req | 1 | O | 复位请求 |

| reset_src_gen | 12 | O | 需要复位的数据包(表示解码后已发送完毕) |

| reset_info_vld | 1 | O | 复位信息有效 |

| reset_ack | 1 | I | 复位请求响应 |

| dcod_data_0 | 64 | O | 输出的IP数据包的数据总线 |

| dcod_ctrl_0 | 8 | O | 输出的IP数据包的控制总线 |

| wr_vld_0 | 1 | O | 输出有效 |

| wr_rdy_0 | 1 | I | 发送数据允许标志 |

| sram_addr | 19 | O | Sram读/写地址 |

| sram_we | 1 | O | Sram写使能 |

| sram_bw | 4 | O | SRAM写入控制信号 |

| sram_wr_data | 36 | O | SRAM写数据总线 |

| sram_rd_data | 36 | I | SRAM读数据总线 |

| sram_tri_en | 1 | O | SRAM写三态控制 |

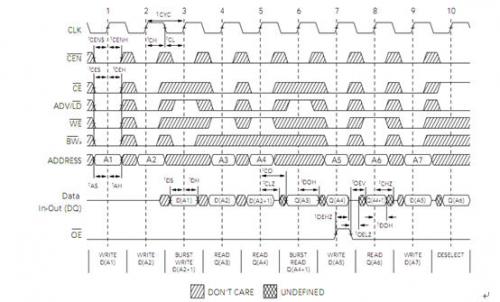

SRAM的读写时序如图3.4-22:

图3.4-22 SRAM读写时序

4 结论

网络编码从提出到现在已有十年,在这期间,网络编码的理论研究和工程应用不断发展和成熟,基于网络编码的多信源组播系统是网络编码在硬件方面的实现。它突破了以往网络编码的应用研究只停留在软件和虚拟网络,通过搭建实际的组播通信网络,并应用NetFPGA平台使网络编码在硬件中得以实现。

文档的前面分别介绍了网络编码的基本概念和研究动态、编解码策略和算法以及编码、转发、解码三个系统的详细设计方案,包括系统的软硬接口和软件的基本功能。由于系统中的网络编解码都是由硬件完成,软件的功能主要是控制和测试时使用,因此方案设计以硬件为主。

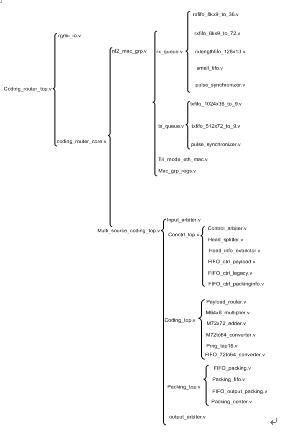

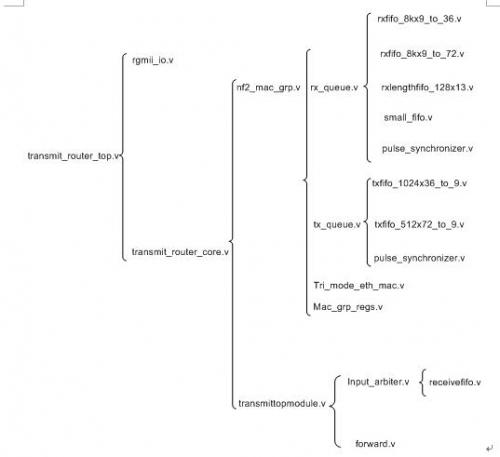

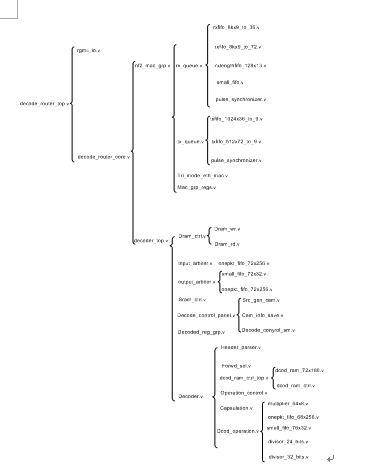

图4-1,图4-2和图4-3分别是编码、转发以及解码路由器三个系统的verilog代码树状图,除去MAC层和core generator产生的代码,代码量有11,000行。附录给出了编码路由器和解码路由器中的关键代码。

图4-1 编码路由器代码树状图

图4-2 转发路由器代码树状图

图4-3 解码路由器代码树状图

附录

附1:编码路由器核心代码:编码模块: payload_router.v

/////////////////////////////////////////////////////////////////////////////

// vim:set shiftwidth=3 softtabstop=3 expandtab:

// Copyright(c) 2009, All rights reserved.

// Advanced Network technology Lab, Shenzhen graduated school of PKU

// Module: payload_router.v

// Project: nf2_coding.ise

// Time and Author: 2009-12-25 liyining

// Description:determine whether should carry out coding operation, and route

// the packets

/////////////////////////////////////////////////////////////////////////////

`define DLY 1

`timescale 1ns/1ns

module payload_router

#(parameter DATAWIDTH = 64,

parameter CTRLWIDTH = DATAWIDTH / 8 //bit-width parameter

)

(

//payload fifo 1 port

input [DATAWIDTH - 1:0] data_payloadfifo_router_1,

input [CTRLWIDTH - 1:0] ctrl_payloadfifo_router_1,

input empty_payloadfifo_router_1,

output reg rd_en_payloadfifo_router_1,

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)