面向大众市场的千兆位级收发器

由于市场对带宽需求的不断增长,设计人员逐步放弃了采用并行总线和低速收发器,转而使用基于串行收发器的接口。因为高速信号可以解决许多设计上的挑战:它们能提供更大的带宽并降低整个系统的成本和功耗。

以上事实使工程师们认为,通过无限地提高收发器的速度,来降低整个系统的成本和功耗。但是,当收发器的速度超过3Gbps后,在某些情况下,其面临的工程挑战会出现本质上的变化,这使得降低整个系统的成本和功耗变得十分困难。其原因十分简单:在超高速的情况下,维持信号完整性的难度将越来越大,有时解决这些问题所做的额外努力要超过数据速率增加所带来的好处。

转变中的收发器

图1显示了传统背板通道的频率损耗和串扰情况。在1.6GHz时,损耗可以被合理地控制,使得速率等于或低于3.2Gbps的收发器相对具有成本效率和功耗优势。

但是,在3GHz时,损耗变得十分显著。这使得速率为6Gbps的背板式收发器需要利用许多不同的特性。你可能需要判决反馈均衡(DFE)这样的先进技术来维持信号的完整性,实现这些先进功能需要利用众多优化特性。

这就是为什么3Gbps收发器通常每个通道只消耗不到100mW的功率,而采用DFE技术的6Gbps收发器却要消耗至少两倍的功耗的原因。对于需要这些先进特性的应用,这一额外的功耗开销是值得的。但如果能同时为尖端应用提供低功耗3.2Gbps收发器和高性能收发器,将会凸显出优势--从本质上为应用提供最佳工具。

在5GHz时,信噪比(SNR|0">SNR)变为负值。在此情况下,需要使用更昂贵的材料和更尖端的制造技术来重新设计整个背板,来为10Gbps的传输创造条件。因此,通过背板实现10Gbps的串行传输会导致在芯片面积和功耗这两方面成本的提高。

前面的例子清楚地显示了工作速率等于或低于3.2Gbps的收发器处于"最佳工作区域",在大多数互联应用中,它们比并行接口和超高速收发器(6Gbps和10Gbps)具有更高的成本效率和功耗优势。这一现象导致收发器市场出现了两种不同的趋势:

Virtex-5 RocketIO GTP收发器

赛灵思清楚地认识到高性能市场的特殊要求,并且注意到大规模主流市场的不同要求。大量主流串行协议的数据率等于或低于3.2Gbps,例如PCI Express Generation 1、千兆以太网、XAUI、SATA|0">SATA I和II、串行 RapidIO、CPRI|0">CPRI、OBSI和HD-SDI。许多像JEDEC数据转换接口和VESA显示端口这样的新兴协议也运行在这种相对较低的数据率下。事实上,这些已有的和新兴的协议涵盖了目前超过90%的收发器应用。因此,速率等于或低于3.2Gbps的收发器是"面向大众市场的收发器"。

赛灵思采取了创新举措,为VirtexTM-5 FPGA系列产品开发了两款不同的收发器。其中一款收发器是Virtex-5 RocketIOTM GTP收发器,主要用于大规模主流应用,其数据率范围从100Mbps到3.2Gbps。面向大多数系统设计人员的GTP收发器具有通用性、易用性、低功耗和低成本特性。

GTP收发器的用途非常广泛,不仅能支持像PCI Express Wrapper这样基于8B/10B编码的协议,还能支持像SONET这样基于加扰编码的协议。(表1给出了GTP收发器所支持的完整应用。)因此,GTP收发器所能支持的应用范围是不受限制的。此外,应用专用设置中对GTP收发器的确认和描述,能确保其符合标准。这些设计和特征化途径共同确保了GTP收发器的通用性。

由于得到了最好的FPGA CAD工具的支持,GTP收发器的使用十分简单。赛灵思®Virtex-5 RocketIO GTP收发器向导提供了直观的GUI界面,为选择GTP、时钟选项、FPGA构造块接口、协议栈以及编解码机制提供了便利。在完成所有选择之后,工具将生成一个带有必要功能的GTP包裹器。

|

图1 - 通道S参数和串扰

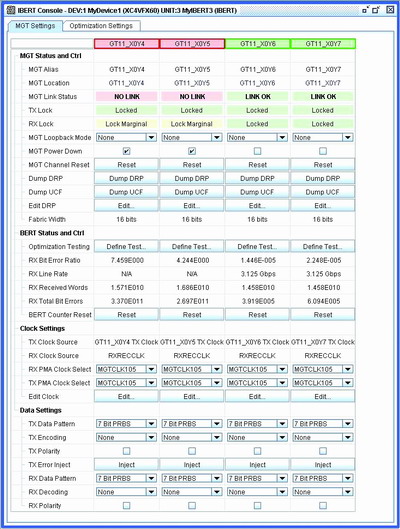

图2 - ChipScope IBERT控制台 赛灵思 ChipScopeTM分析器通过内置在收发器里的集成式误比率测试器(IBERT),向GTP收发器提供自测试能力。图2显示了ChipScope IBERT控制台。ChipScope分析器所提供的先进功能包括通道性能测量能力、自动眼图扫描能力(用来寻找最佳的发送和接收设置)以及收发器和连接状态报告。这些丰富的工具大大简化了基于GTP收发器的设计和制造流程,对于GTP收发器的广泛应用起到了关键的促进作用。 随着PCB板上的空间越来越拥挤,收发器的功耗成为一个关键问题。因此,对于GTP收发器来说,电源效率是最首要的设计目标之一。每个GTP收发器的平均功耗通常低于100mW。在某些情况下,每个收发器的功耗能低至60mW。对于低功耗的广泛需求进一步增强了GTP收发器在功耗敏感型应用中的竞争力。 随着大规模主流应用开始使用嵌入式收发器,成本也成为一项重要的考虑因素。因此,赛灵思用硬逻辑而不用查找表(LUT)的方法来提供某些特定的解决方案。例如,一种硬件编码的PCI Express协议栈包括基于GTP收发器的物理层、链路层和应用层。这一实现方案极大地降低了整个解决方案的成本,使得基于GTP收发器的解决方案对于大容量/高利润应用更具吸引力。 |

SNR DFE FPGA CPRI SATA PCI GTP 相关文章:

- 德州仪器推出高性能双/四通道 ADC 产品系列(03-23)

- 100G DWDM,深度优化OSNR的技术 (03-10)

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)