基于网络编码的多信源组播通信系统,包括源代码,原理图等

| 2 | O | 解码数据包的所存储的RAM号 | |

| coef_mut | 8 | O | 乘法系数 |

| coef_div | 8 | O | 除法系数 |

| cap_info_req | 1 | I | 封装信息请求 |

| dcod_comp | 1 | I | 解码封装完成 |

| cap_info_vld | 1 | O | 封装信息有效 |

| need_feed_back | 1 | O | 需要反馈 |

| pkt_len | 16 | O | 数据包长度 |

| src_num | 4 | O | 数据包的信源号 |

| gen_num | 8 | O | 数据报的代编号 |

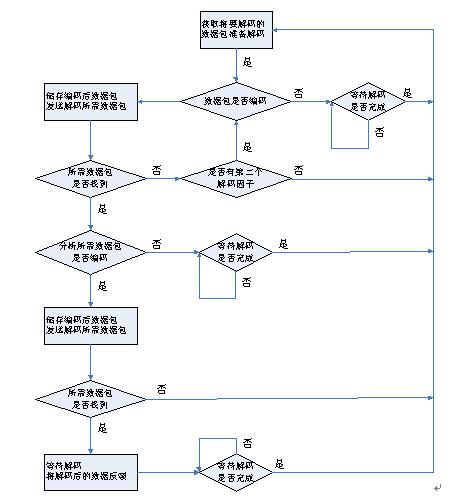

Operation_control模块的主要功能是:接收header_parser发送过来的数据,通过计算和比较后与decode control panel通信,告诉decode control panel解码所需要的数据包和解码完成标志;给RAM读写给出RAM号(即存储在哪个RAM中);给decode operation模块提供解码所需要的系数和RAM号;给capsulation模块提供源IP和是否需要反馈数据的命令,其控制状态如图3.4-19下:

图3.4-19:Operation_control状态机处理流程

⑤ decode operation

decode operation是解码运算模块,它将来自fwd_sel模块的未编码的数据和来自RAM的编码数据完成减法和除法运算,还原被编码的数据。解码后将数据总线的位宽恢复为64bits。解码运算模块的端口列表如下:

| 信号名称 | 位宽bits | I/O | 信号描述 |

| dcod_payload | 64 | O | 解码后的数据包的有效载荷 |

| end_payload | 4 | O | 数据包结束标志,指明最后一个有效字节 |

| payload_vld | 1 | O | 输出数据有效 |

| wr_rdy | 1 | I | 输出数据允许信号 |

| uncod_data_vld | 1 | I | 输入至dcod_operation的数据有效 |

| uncod_data_factor | 64 | I | 输入至dcod_operation的数据总线 |

| uncod_data_eop | 4 | I | 数据包结束标志,指明最后一个有效字节 |

| dcod_rdy | 1 | O | 输入至dcod_operation允许信号 |

| rd_ram_num | 2 | O | 需要读取数据的RAM号 |

| rd_req | 1 | O | 读RAM请求 |

| ram_data_eop | 4 | I | 数据包结束标志,指明最后一个有效字节 |

| ram_data | 72 | I | 读RAM的数据总线 |

| ram_vld | 1 | I | 读RAM数据有效 |

| rd_info_req | 1 | O | 读取解码信息请求 |

| dcod_info_vld | 1 | I | 解码信息有效 |

| ram_num | 2 | I | 解码数据包的所存储的RAM号 |

| coef_mut | 8 | I | 乘法系数 |

| coef_div | 8 | I | 除法系数 |

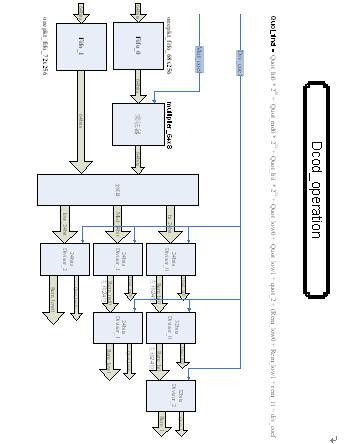

为了快速完成解码运算,我们在此采取并行除法的方法使之能快速解码,解码运算的算法图如图3.4-20:

图3.4-20 decoder_operation内部的并行除法

⑥ capsulation

Capsulation是解码运算的最后一个模块,其主要功能是封装解码后的数据包。其主要任务是:(1)接收来自decode operation和header_parser的

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)