基于网络编码的多信源组播通信系统,包括源代码,原理图等

② cam_info_save:

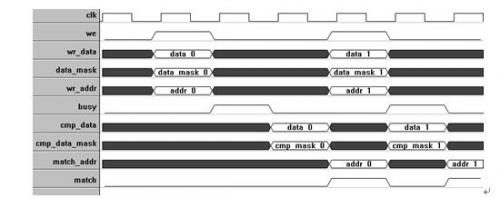

该模块的主要功能是将输入的数据包的信源号和代的编号按地址大小顺序存入到三个cam中,每个cam分别对应于三个数据输入通道。每个CAM的大小是24bits×256,我们要求CAM的读写操作可以同时进行,写数据从DIN进入,而读(查询)的数据从CMP_DIN进入,写操作时BUSY信号有效,表示不可以响应其他写请求,图3.4-12是一个CAM的读写操作时序:

图3.4-12:CAM读写过程

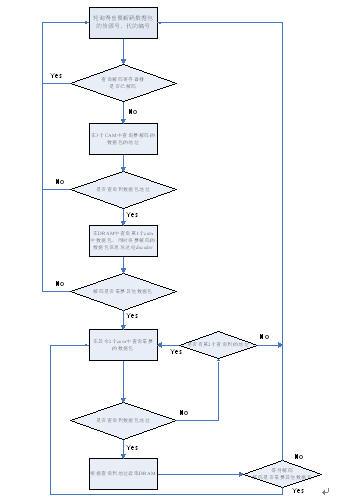

③decode_control_sm

该模块的功能是按照轮询策略,控制decoder解码储存在DRAM中的数据包。通过查询CAM中的数据包的存储地址,将查询到的地址输出给DRAM读写控制模块,从而找到解码所需要的数据,同时将要查询的数据包的信源号和代的编号发送给解码模块。若不能查找到解码因子,则将信号Pkt_not_find置为有效电平,通知decoder无法解码,同时将状态转到解码下一个数据包的状态上。在开始查找CAM时,要等待储存一定数量的数据包,在我们的系统里面,暂定为32。

状态机处理控制流程如图3.4-13:

图3.4-13:decode_control_sm状态机及数据处理流程

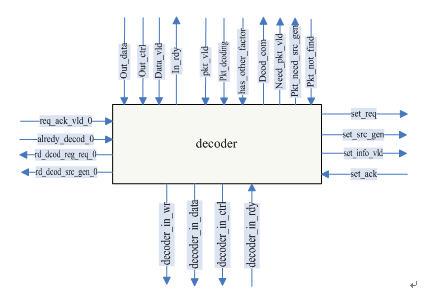

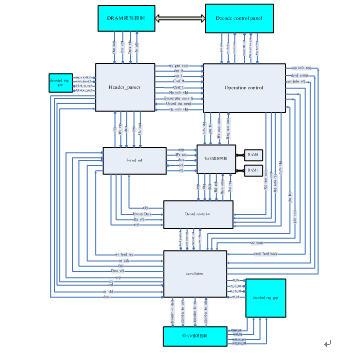

6、decoder

decoder是整个解码路由器的核心之一,它的主要功能是接收来自DRAM的编码后的IP数据包,在decode_control_panel模块的控制下对数据包进行解码,它包括多个小模块,其整体图和内部结构图如3.4-14和3.4-15所示:

图3.4-14 decoder整体结构图

图3.4-15:decoder内部结构图

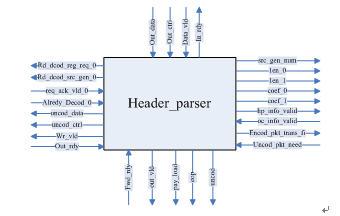

① header_parser

分析接收到的数据包,如果已经被编码,根据包头提取信源号、代号、长度和系数给运算控制模块,如果没有被编码,则查询解码标志寄存器,如果已经解码并储存在二级缓存中,则该数据包只是一个解码因子,把数据发送到fwd_sel,若没有解码,则同时发送到capsulation和forward sel。如果数据是编码后的数据包,则将数据包去掉包头后将数据发送给forward sel模块。当发送到最后的64位数据时,eop信号有效,指明是数据包的最后有效字节。

下图所示为输入输出接口图3.4-16:

图3.4-16:header_parser模块图

其输入输出端口列表如下:

| 信号名称 | 位宽bits | I/O | 描述 |

| in_rdy | 1 | O | 数据输出输入允许信号 |

| out_data | 64 | I | 输入的数据包的data_bus |

| out_ctrl | 8 | I | 输入数据包的ctrl_bus |

| data_vld | 1 | I | 输入数据有效 |

| rd_dcod_reg_req_0 | 1 | O | 读取解码标志位请求 |

| rd_dcod_src_gen_0 | 12 | O | 要读取的数据包的信源号和代编号 |

| req_ack_vld_0 | 1 | I | 输入有效 |

| alredy_decod_0 | 1 | I | 解码标志("1"代表已经解码,"0"代表未解码) |

| Uncod_data | 64 | O | 未编码数据包的数据总线 |

| Uncod_ctrl | 8 | O | 未编码数据包的控制总线 |

| Wr_vld | 1 | O | 写capsulation数据有效 |

| Out_rdy | 1 | I | 输出capsulation允许信号 |

| fwd_rdy | 1 | I | 输出fwd_sel允许信号 |

| out_vld | 1 | O | 输出fwd_sel有效 |

| pay_load | 64 | O | 输出fwd_sel数据(不含包头) |

| eop | 4 | O | 最后指示一个有效字节的指示 |

| uncod | 1 | O | 指明输出的数据包是否编码 |

| src_gen_num | 12 | O | Decoder接收到的数据包的信源号和代的编号 |

| len_0 | 16 | O |

|

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)