基于网络编码的多信源组播通信系统,包括源代码,原理图等

| Request Negotiation | p_wr_ptr | from user logic to block-of-data rd/wr module | PKT_MEM_PTR_WIDTH | the start address of DRAM for transfer. Each unit is 16-byte piece |

| Request Negotiation | p_wr_ack | from block-of-data rd/wr module to user logic | 1 | 1=the arbiter acknowledges that the write requester can proceed, 0=otherwise |

| Data Transfer | p_wr_data_vld | from user logic to block-of-data rd/wr module | 1 | 1=the write data is valid, 0=otherwise |

| Data Transfer | p_wr_data | from user logic to block-of-data rd/wr module | PKT_DATA_WIDTH | the data transferred from user logic to DRAM |

| Data Transfer | p_wr_full | from block-of-data rd/wr module to user logic | 1 | 1=notify the user logic to pause transfer the next clock cycle until this signal is deasserted, 0=otherwise |

| Data Transfer | p_wr_done | from block-of-data rd/wr module to user logic | 1 | 1=this is the last write and no more write will be accepted for this block-of-data, 0=otherwise |

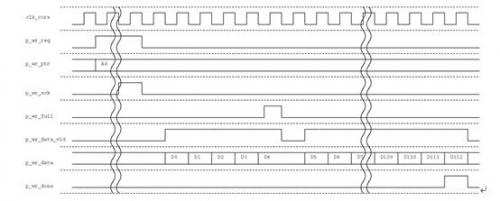

写DRAM时序如图3.4-7:

图3.4-7 写DRAM时序图

读端口:

| Signal Group | Signal Name | Direction | Bits | Description |

| Request Negotiation | p_rd_req | from user logic to block-of-data rd/wr module | 1 | 1=request for read transfer (data are from DRAM to user logic), 0=otherwise |

| Request Negotiation | p_rd_ptr | from user logic to block-of-data rd/wr module | PKT_MEM_PTR_WIDTH | the start address of DRAM for transfer. Each unit is 16-byte piece |

| Request Negotiation | p_rd_ack | from block-of-data rd/wr module to user logic | 1 | 1=the arbiter acknowledges that the read requester can proceed, 0=otherwise |

| Data Transfer | p_rd_rdy | from block-of-data rd/wr module to user logic | 1 | 1=block-of-data rd/wr module has data for user logic to read, 0=otherwise |

| Data Transfer | p_rd_en | from user logic to block-of-data rd/wr module | 1 | 1=user logic reads out one word of data from the block-of-data rd/wr module, 0=otherwise |

| Data Transfer | p_rd_data | from block-of-data rd/wr module to user logic | PKT_DATA_WIDTH | data transferred from block-of-data rd/wr module to user logic |

| Data Transfer | p_rd_done | from block-of-data rd/wr module to user logic | 1 | 1=this is the last read data and no more data will be read for this block-of-data, 0=otherwise |

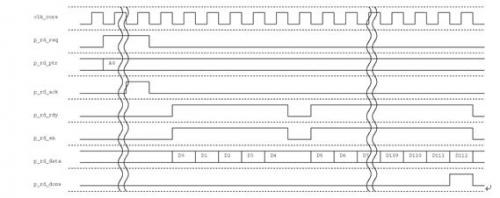

读DRAM时序如图3.4-8:

图3.4-8 写DRAM时序图

② 其他模块对DRAM控制器的读/写过程:

当DRAM读写控制器将一个数据包读/写完之后, 就将rd_idle/wr_rdy_arb置为1,当外部模块需要对DRAM进行读写时,首先要判断这两个信号是否有效,在有效的情况下进行对数据的操作。.端口列表如下:

| 信号名称 | 位宽bits | I/O | 描述 |

| wr_vld_arb | 1 | I |

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)