基于网络编码的多信源组播通信系统,包括源代码,原理图等

| 1 | I | 写有效 | |

| wr_rdy_0 | 1 | O | 接收数据空闲标志 |

| non_ip_data | 64 | I | 非IP数据包数据总线 |

| non_ip_ctrl | 8 | I | 非IP数据包控制总线 |

| wr_vld_1 | 1 | I | 写有效 |

| wr_rdy_1 | 1 | O | 接收数据空闲标志 |

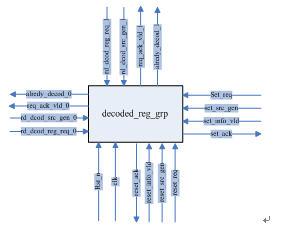

3、decoded_reg_grp

本模块分别与decode_control_panel,decoder和SRAM_contrl相连接,主要作用是记录信源的某代数据包是否已经解码,并将相应的解码信息输出给其他模块,模块结构如图3.4-3:

图3.4-3:decoded_reg_grp模块图

端口列表:

| 信号名称 | 位宽bits | I/O | 描述 |

| rd_dcod_reg_req_0 | 1 | I | 读取解码标志位请求 |

| rd_dcod_src_gen_0 | 12 | I | 要读取的数据包的信源号和代编号 |

| req_ack_vld_0 | 1 | O | 输出有效 |

| alredy_decod_0 | 1 | O | 解码标志("1"代表已经解码,"0"代表未解码) |

| rd_dcod_reg_req_1 | 1 | I | 读取解码标志位请求 |

| rd_dcod_src_gen_1 | 12 | I | 要读取的数据包的信源号和代编号 |

| req_ack_vld_1 | 1 | O | 输出有效 |

| alredy_decod_1 | 1 | O | 解码标志(为1时代表已经解码,为0时未解码) |

| set_req | 1 | I | 置位请求 |

| set_src_gen | 12 | I | 需要置位的数据包(表示已经解码完毕) |

| set_info_vld | 1 | I | 置位信息有效 |

| set_ack | 1 | O | 置位请求响应 |

| reset_req | 1 | I | 复位请求 |

| reset_src_gen | 12 | I | 需要复位的数据包(表示解码后已发送完毕) |

| reset_info_vld | 1 | I | 复位信息有效 |

| reset_ack | 1 | O | 复位请求响应 |

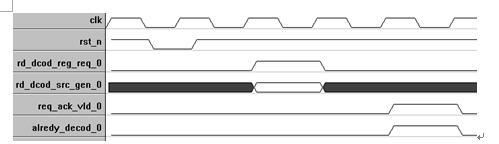

① 读解码标志

当decoder模块或decode_control_panel读取解码标志时,将查询结果输出,alredy_decod_0和alredy_decod_1为"1"时表示本次查询的数据包已经解码,为"0"时表示未被解码,以与decoder接口为例,读取解码标志的时序如图3.4-4:

图3.4-4:读解码标志位时序图

② 写解码标志位

当decoder把一个数据包解码成功后,就把相应的解码标志位置1,当SRAM_control将一个数据包发送出去后,再将相应的解码标志位置0,以置位为例,解码标志位的写时序如图3.4-5:

图3.4-5:置位解码标志寄存器

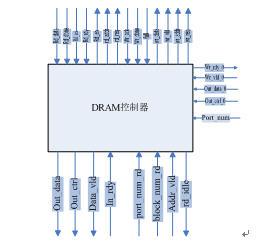

4、DRAM控制器:接收数据,并顺序存储到DRAM中去。

注意:我们将DRAM分为三块,分别对应于数据接收的三个信道,即第0个信道的数据存储到DRAM的第0块,第1个信道的数据存储到DRAM的第1块……信道号由port_num给出。由于DRAM是按照block读写的,因此每个block大小为2034字节,位宽为144位。

图3.4-6:DRAM控制器模块图

① DRAM控制器与DRAM的接口与读写时序:

| Signal Group | Signal Name | Direction | Bits | Description |

| Request Negotiation | p_wr_req | from user logic to block-of-data rd/wr module | 1 | 1=request for write transfer (data are from user logic to DRAM) |

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)