基于网络编码的多信源组播通信系统,包括源代码,原理图等

| Rdy_router_packingfifo | 1 | Output | 1=module "packing FIFO" is ready to receive from payload router, 0=otherwise |

| Router_status | 3 | input | Input FSM state signal to coordinate with the control of "packing FIFO" |

| Empty_packingfifo | 1 | output | 1=FIFO packing is empty,0=otherwise |

| Data_converter_packingfifo | 73 | input | Input data bus from "m72to64 converter". Bit 64 is set to "1" to indicate this is a coded packet |

| Wr_en_converter_packingfifo | 1 | Input | Write enable |

| Rdy_converter_packingfifo | 1 | Output | 1=module "packing FIFO" is ready to receive from m72to64 converter, 0=otherwise |

| Empty_converterfifo | 1 | Input | 1=FIFO converter is empty,0=otherwise |

| Data_center_legacyfifo_1 | 64 | Input | Input data bus from "FIFO ctrl legacy 1" |

| Rd_en_center_legacyfifo_1 | 1 | output | Read enable |

| Data_center_packinginfo_1 | 14 | Input | Input data bus from "FIFO ctrl packinginfo 1" |

| Rd_en_center_packinginfo_1 | 1 | output | Read enable |

| Data_center_legacyfifo_2 | 64 | Input | Input data bus from "FIFO ctrl legacy 2" |

| Rd_en_center_legacyfifo_2 | 1 | output | Read enable |

| Data_center_packinginfo_2 | 14 | Input | Input data bus from "FIFO ctrl packinginfo 2" |

| Rd_en_center_packinginfo_2 | 1 | output | Read enable |

| Rand_num_center_1 | 8 | input | Input random number from "m64×64 multiplier 1" |

| Rand_num_center_2 | 8 | input | Input random number from "m64×64 multiplier 2" |

| Out_data_out_0 | 64 | output | Output data bus to "output arbiter" |

| Out_ctrl_out_0 | 8 | Output | Output ctrl bus to "output arbiter" |

| Data_val_out_0 | 1 | Output | 1=data from packing center to output arbiter is valid, 0=otherwise |

| Rdy_out_0 | 1 | Input | 1=output arbiter is ready to receive from packing center, 0=otherwise |

| clk | 1 | Input | System clock running at 125 MHz |

| Rst_n | 1 | input | System asynchronous reset signal |

④ 功能描述及数据流

本模块为封装模块。子模块packing FIFO构建与coding模块的数据接口,将接收并缓存编码数据包以及未编码数据包(使用额外第64位数据标志该包是否编码,该位为"1"说明编码,该位为"0"说明未编码)。

子模块packing center是主封装模块。它根据packing FIFO中读出的数据判断需要哪些包头信息,然后向control模块中相应FIFO读取需要的包头信息,并依次封装成NCP数据包,发送到output arbiter。

⑤ 关键时序及状态机

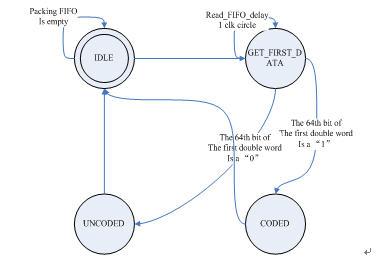

Packing center状态机第一层状态机:packing_center_status

图3 .2-9 packing_center_status状态机

第二层状态机:

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)