基于网络编码的多信源组播通信系统,包括源代码,原理图等

| Control_arbiter | 1 | Detect ctrl bus to determine whether should process both channels synchronously or hold one channel and process the other. |

| FIFO ctrl payload | 2 | Standard FIFO generated by CoreGen, store payload |

| FIFO ctrl legacy | 2 | Standard FIFO generated by CoreGen, store legacy head |

| FIFO ctrl packinginfo | 2 | Standard FIFO generated by CoreGen, store packing info head |

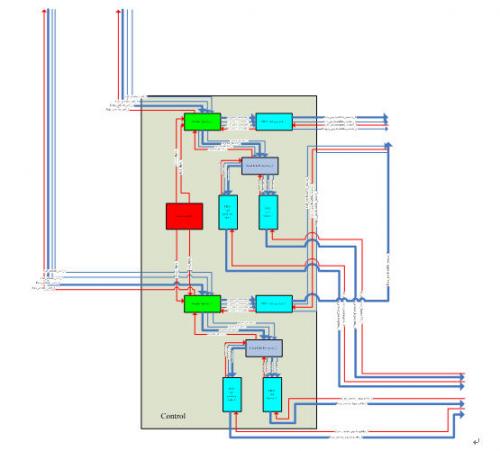

② 内部结构如图3.2-4

图3.2-4:control模块内部结构

③ 本模块输入输出信号列表及说明

| Signal name | Bit width | Input or output | description |

| Data_arbiter_ctrl_1 | 64 | Input | Input data bus from "input arbiter 1" |

| Ctrl_arbiter_ctrl_1 | 8 | Input | Input ctrl bus from "input arbiter 1" |

| Val_arbiter_ctrl_1 | 1 | Input | 1=data from input arbiter 1 to head splitter 1 is valid, 0=otherwise |

| Rdy_arbiter_ctrl_1 | 1 | output | 1=module "head splitter 1" is ready to receive from input arbiter 1, 0=otherwise |

| Data_arbiter_ctrl_2 | 64 | Input | Input data bus from "input arbiter 2" |

| Ctrl_arbiter_ctrl_2 | 8 | Input | Input ctrl bus from "input arbiter 2" |

| Val_arbiter_ctrl_2 | 1 | Input | 1=data from input arbiter 2 to head splitter 2 is valid, 0=otherwise |

| Rdy_arbiter_ctrl_2 | 1 | output | 1=module "head splitter 2" is ready to receive from input arbiter 2, 0=otherwise |

| Data_payloadfifo_router_1 | 64 | output | output data bus to "payload router" |

| Ctrl_payloadfifo_router_1 | 8 | output | Output ctrl bus to "payload router" |

| Rd_en_payloadfifo_router_1 | 1 | Input | Read enable |

| Empty_payloadfifo_router_1 | 1 | output | 1=FIFO ctil payload 1 is empty,0=otherwise |

| Data_payloadfifo_router_2 | 64 | output | output data bus to "payload router" |

| Ctrl_payloadfifo_router_2 | 8 | output | Output ctrl bus to "payload router" |

| Rd_en_payloadfifo_router_2 | 1 | Input | Read enable |

| Empty_payloadfifo_router_2 | 1 | output | 1=FIFO ctrl payload 2 is empty,0=otherwise |

| Data_center_legacyfifo_1 | 64 | Output | Output data bus to "packing center" |

| Rd_en_center_legacyfifo_1 | 1 | Input | Read enable |

| Data_center_packingfifo_1 | 14 | Output | Output data bus to "packing center" |

| Rd_en_center_packingfifo_1 | 1 | input |

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)