基于网络编码的多信源组播通信系统,包括源代码,原理图等

的算法和协议,或者处理一些异常情况,同时,对于系统开发人员,也应该是可控的,因为开发人员往往需要配置和调试硬件。使用通用的寄存器接口就可以使数据处理对软件透明化,这是靠映射内部的硬件寄存器来完成的,即所谓的存储映射技术。对于软件来讲,映射寄存器相当于一个I/O接口,它可以由软件访问和修改。

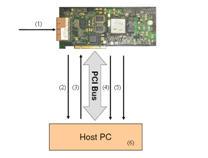

图2.5-1:系统中的register bus 和data bus

Register bus中每个模块的register连接在一起,组成一个信息环路。这些register块中存储了数据处理在每个模块中的状态和阶段,任何一个模块都可以响应来自PCI总线寄存器的访问和控制要求,而PCI总线寄存器可以通过软件来控制。也就是说,硬件和软件的通信是通过PCI总线完成的。

数据以及控信息在硬件和主机系统之间是通过PCI总线传输的,以Linux网络存储栈作为接口的。NetFPGA向主机发送分组数据的过程如图2.5-2a所示:

分组到达,发往CPU队列; 中断程序通知驱动程序有分组到达; 驱动程序设置和初始化DMA传送器; NetFPGA通过DMA总线发送分组; 中断程序发送DMA结束信号; 驱动程序把分组传递到网络存储栈;

图2.5-2a:NetFPGA向主机发送数据 图2.5-2b:主机向NetFPGA发送数据

主机向NetFPGA发送分组数据的过程如图2.5-2b所示:

控制软件通过网络socket发送分组,分组被递交给驱动程序; 驱动程序设置和初始化DMA传送器; 中断程序发送DMA结束信号;主机访问寄存器是通过系统调用系统内核的ioctl( )函数作为接口的。读写寄存器的操作函数如下,这两个函数内部调用了ioctl( )函数。

readReg(nf2device *dev, int address, unsigned *rd_data)

writeReg(nf2device *dev, int address, unsigned *wr_data)

例如: readReg(&nf2, OQ_NUM_PKTS_STORED_0, &val);

主机访问NetFPGA寄存器的过程如下:

(1)控制软件调用ioctl( )函数操作网络socket,由函数ioctl传递给驱动程序;

(2)驱动程序完成PCI寄存器的读写;

3 系统的详细设计方案

3.1 概述

在组播网络的拓扑图中,编码路由器、转发路由器和解码路由器是三个独立的系统,各自完成编码、转发和解码的任务。前面讲过,分组的编码、解码主要在网络层完成。在网络层中数据通道中,data bus和ctrl bus是同步传输的,二者之间的关系和格式如图3.1-1所示:

| ctrl bus(8位) | Data bus(64位) |

| ff | module header |

| 00 | Pkt data1 |

| 00 | …… |

| xy(xy≠00) | Last pkt data |

图3.1-1 数据通道中的data bus和ctrl bus

Ctrl为ff时,表明为一个数据包的包头,xy为非零数据,指明最后一个有效的字节所在的位置,如01000000指明是第7个,即data[63:48]为有效数据。模块之间数据传输的过程是:若上一个模块已经处理完毕,想把数据传输到下一个模块,首先判断输入信号rdy是否有效,当rdy = 1时,将数据和控制信号同步发送出去,同时wr_vld信号有效,时序如图3.1-2所示:

图3.1-2 有效的数据传输时序

3.2 编码路由器详细设计方案

3.2.1编码系统整体模块如图3.2-1所示

图3.2-1:编码系统整体模块图

3.2.2系统中各单元模块的功能与时序

(1)Input arbiter

① Input arbiter内部结构如图3.2-2所示:

图3.2-2 Input arbiter内部结构图

② 本模块输入输出信号列表及说明

| Signal name | Bit width | Input or output | description |

| Input_fifo_data_1 | 64 | input | Input data bus from "input FIFO 1" |

| Input_fifo_ctrl_1 | 8 | input | Input ctrl bus from "input FIFO 1" |

| Input_fifo_empty_1 | 1 | input | 1=input FIFO is empty,0=otherwise |

| Input_fifo_rd_en_1 | 1 | output | Read enable |

| Input_fifo_data_2 | 64 | input | Input data bus from "input FIFO 2" |

| Input_fifo_ctrl_2 | 8 | input | Input ctrl bus from "input FIFO 2" |

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)