基于网络编码的多信源组播通信系统,包括源代码,原理图等

| out_data_0 | 64 | I | 输入的数据包的data_bus |

| out_ctrl_0 | 8 | I | 输入数据包的ctrl_bus |

| port_num_dram | 2 | I | 输入信号的端口号,指明数据存放在DRAM的区域 |

| wr_rdy_arb | 1 | O | 写空闲信号 |

| port_num_rd | 2 | I | 读取数据包的区域 |

| addr_vld | 1 | I | 读地址有效 |

| block_num_rd | 8 | I | 数据包存放的block的起始地址 |

| rd_idle | 1 | O | 读空闲信号 |

| in_rdy | 1 | I | 数据输出输出允许信号 |

| out_data | 64 | O | 读出的数据包的data_bus |

| out_ctrl | 8 | O | 输出数据包的ctrl_bus |

| data_vld | 1 | O | 输出数据有效 |

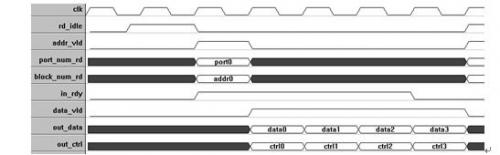

(1)当decode_control_panel对DRAM控制器进行读操作时,将信道号和block地址发送至DRAM控制器,接着DRAM控制器从DRAM中读取数据,当decoder空闲时将数据发送出去,时序图如3.4-9所示:

图3.4-9 对DRAM控制器的读操作

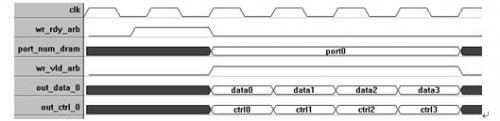

(2)当DRAM控制器进行写操作时,将按照input_arbiter发送过来的端口号,按照地址大小顺序写DRAM,时序图如3.4-10:

图3.4-10 对DRAM控制器的写操作

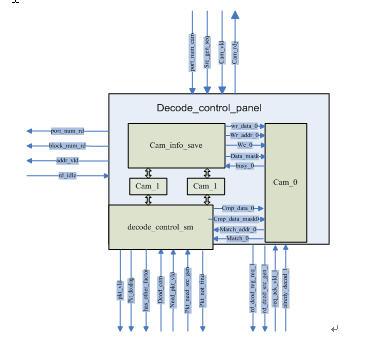

5、decode_control_panel

① 本模块的内部结构图如3.4-11所示,它由以下五个模块组成:cam_info_save, decode_control_sm和3个CAM组成。

图3.4-11:decode_control_panel内部结构图

本模块的输入输出端口定义表如下:

| 端口名称 | 位宽 bits | I/O | 描述 |

| port_num_cam | 2 | In | 数据写入的CAM号,即信道号 |

| Src_gen_seq | 24 | In | 输入数据包的信源号、代编号 |

| Cam_vld | 1 | In | 写有效 |

| Cam_rdy | 1 | Out | 写Cam准备好 |

| rd_idle | 1 | In | DRAM准备好 |

| block_num_rd | 8 | Out | 读DRAM的地址 |

| addr_vld | 1 | Out | 读地址有效 |

| port_num_rd | 2 | out | 要读取的DRAM的编号 |

| Pkt_vld | 1 | Out | 要解码的数据包输出有效标志 |

| Pkt_decoding | 12 | out | 正在解码的数据包的信源号、代编号 |

| Decod_com | 1 | In | 数据包解码完成标志 |

| has_other_factor | 1 | Out | 有另外一个解码因子 |

| Pkt_not_find | 1 | Out | 所需要解码数据包未找到 |

| pkt_need_src_gen | 12 | In | 解码需要的数据包 |

| need_pkt_vld | 1 | In | 所需数据包有效 |

| rd_dcod_reg_req_1 | 1 | Out | 读解码标志寄存器请求 |

| req_ack_vld_1 | 1 | In | 标志位有效 |

| Alredy_Decod_1 | 1 | In | 解码标志位 |

| rd_dcod_src_gen_1 | 12 | out |

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)