dc多时钟综合约束问题

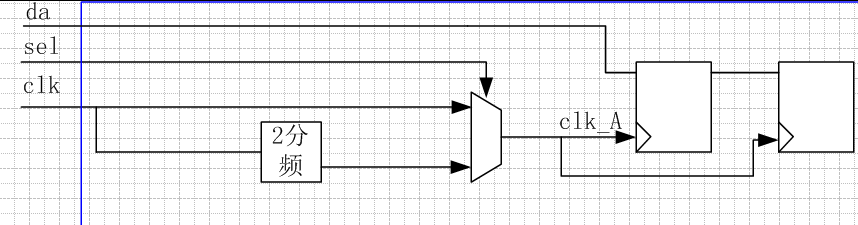

问一下 下面电路DC如何设置时钟约束

create_clock -name clk -period xx -waveform xx [get_ports clk]

create_clock -name clk_div2 -period xx -waveform xx [get_pins xx]

create_generated_clock -name clk_A [get_pins MUX/Z] -source [get_pins xx] -divide_by 1

set_case_analysis x MUX/S

我觉得应该是这样,请高手指正

不乱说。

create_clock -name clk -period xx -waveform xx [get_ports clk]

set_case_analysis x MUX/S--> (select clk)

不需要再设置create_generated_clock

MUX可直接穿过clcok

要么直接在MUX后设create_clock,前面不设

要么前面设create_clock,再设case_analysis

不需要generate_clock

现在这种情况如果要对时钟设置驱动无限大,应该对哪个时钟进行设置呢?

你好请问,

1.为何这里要case_analysis,是为了分析sel为1和为0的不同情况,因此要做两次独立的timing么?

2.为何不将create_generate_clock定义在分频的输出上?因为如果没有generate_clock,那么在case_analysis(sel)到2分频输出的时候,工具如何分析MUX后的寄存器的时钟从哪来?

3.如果不设置case_analysis,那么工具会怎么处理这个mux?时序分析结果是不是就会报告clk的一条路径和div_clk的一条路径?

4.补充一个我自己纠结很久的问题:如下图:如果将REG1定义为generate_clock的pin和将div_clk定义为generate_clock的pin会对时序分析有什么不同的影响?其中“三角形”表示一个buf?如果定义的pin在buf之后,那么将无法分析REG1/Q到REG2/D的时序?

定义分频时钟什么时候需要将reg/Q的后面加上一个buf,从buf上定义分频的pin?

是的,MUX应该是可以传过去的

请问下,你提到的“mux可以穿过去”,是指什么意思?

是说2分频和clk都可以传过去么?

那么是否应该是定义个clk和定义个generate_clock在“2分频”的模块输出上?

不太理解这里的clk_div2为什么用create_clock而不用create_generated_clock -name clk_div2 -source [get_ports clk][get_pins xx]

还烦请给解释一下

我也不懂!~

陳老大, 這麼做的原因是因為兩個clock 是倍頻關係,所以只要constraint 最緊的那一個path就可以了嗎?

這樣的話, 另一條path上可能會是unconstraint的,

path timing的好壞只能修到trans/cap 的限制裡面

但因為是倍頻關係, margin應該比較寬鬆,故應該timing 會pass.

我這樣的理解是正確的嗎?

p.s. 會這樣問的原因是因為我們上次遇到這種情況

一開始採用你的做法, 但發現case掉的另一條path會很糟

但有可能是因為我們的兩個clock為異步時鐘.

这样做,在timing report 报告中,不能追到最前面的时钟起始点吧?

请问这是什么,怎么用的,你知道怎么调用dc中的门控时钟模块么?