时钟同时又作为数据输入该如何约束?

时间:10-02

整理:3721RD

点击:

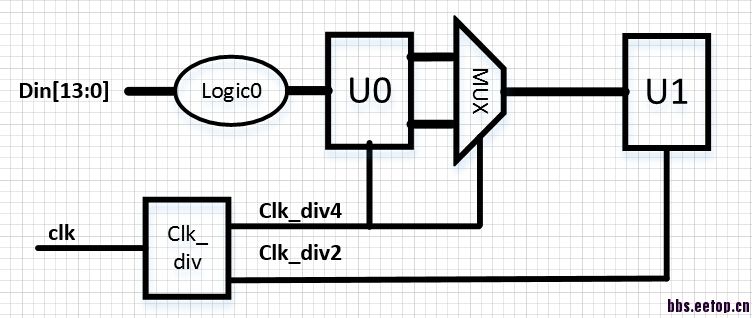

如图,这是一个时钟信号同时又充当数据输入的问题,它作为mux的选择信号,同时又加上包含了两个同步时钟域的问题,感觉处理起来比较费解,希望有人能给出令人信服的解决方案。

1. 同步多时钟域的问题在我的另一个问题中已有讨论:同步多时钟域问题

2. 这个问题,有一个解决方法是将clk_div2后面接一个buffer,假设buffer后面的net命名为clk2_net,对clk2_net进行generated clock,而原先的数据通道则默认为数据的处理。那么添加buffer是直接在RTL代码中添加还是在DC综合后的网表中添加好呢?

这个设计是不是可以改成都工作在 clk_div2下,用clk_div2做一个一bit mux选择信号。感觉一个时钟足够了。

本来是一个HBF插值滤波器,我把它简化成这样子了。只用一个时钟是不太现实的吧!