如何约束某一分频时钟,急求

代码描述为:clk8 = ~clk_cnt[2];

clk8为div_clk模块的output;clk_cnt是在clk下的一个计数器;因此clk8为clk的八分频,并且翻转后的时钟

问题

create_generated_clock -divide_by 8 -invert -name clk8 -source clk [get_pins div_clk/clk8]

红色表示出的-invert是否需要?

考虑到需要翻转的应该是clk_cnt[2]的寄存器值,我私以为如果使用 get_pins div_clk/clk8 应该是不需要这个-invert吧?只有使用get_nets div_clk/clk_cnt[2]才需要-invert?

求助各位应该如何约束这个分频时钟?

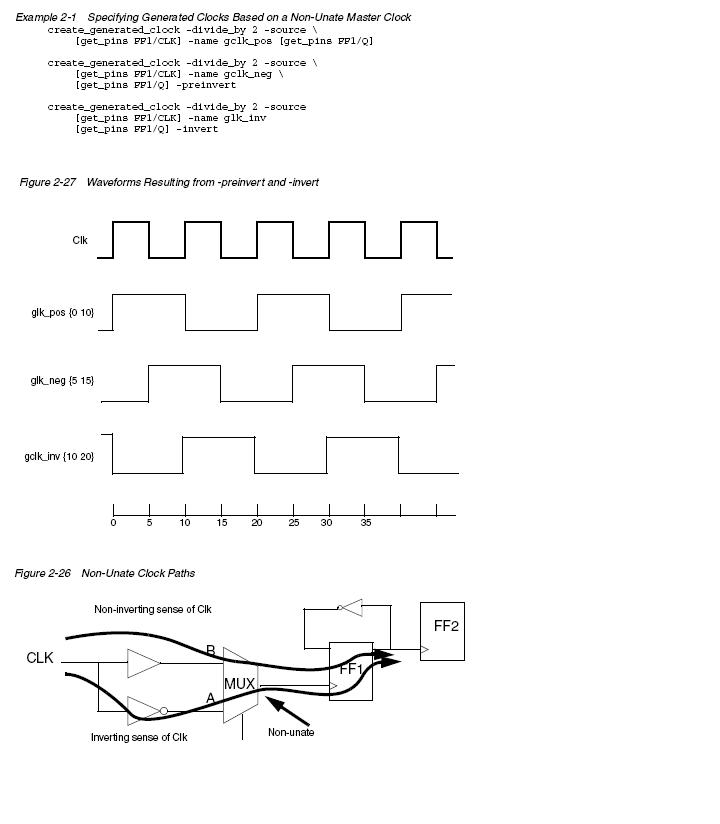

invert 是看你source clk的沿和div clock的沿的关系 是你定义好的

为啥要clk8 = ~clk_cnt[2] 为啥不是clk8 = clk_cnt[2],这个能讲清楚,那么沿的问题就能想明白

我不太明白你的意思啊?能否说明些?

我的理解就是因为代码中有取反。所以就需要一个invert的选项

画一下clk 和这个 cnt[2] 以及~cnt[2]的波形,然后分别找你认为设计需要check setup的两个clk 沿,然后看看DC报的timing是否和你预想的沿一致。

如果不是你设计的代码,你可以问一下设计者在这里的clk 相位是怎么考虑的

之所以要取反是为了在逻辑的处理更加方便,

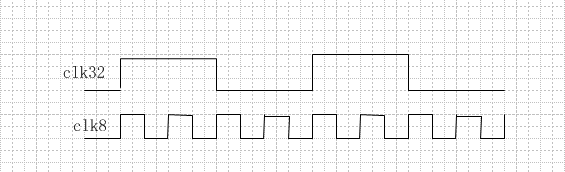

对于设计中有另外一个分频clk32 = clk_cnt[4];对比其和clk8=~clk_cnt[2]的波形,由于clk32和clk8的时钟域下的数据有交互,那么是否应该要加个invert?至于你说的画波形确定需要比较的是哪两个时钟沿,我不太清楚应该如何处理。退一步讲,如果clk8是没有取反的,那么我可能直接就create_generated_clock去生成两个clk8和clk32了,也不会考虑要画一个波形。

我私以为,如果我不加这个invert 选项,那么clk8的波形就恰好是上图中的取反结果,

那么我想,这将和我代码中的clk8取反并且always @ (posedge clk8)所需要表述的时刻点肯定是不相符的,因此我认为你应该是要加-invert这个选项

不好意思,帖子刚才编辑了下,把时序图弄上去

这两个设置报timing所用的clock margin都是一个clk8的period,只是报出来的waveform的点不一样,

逻辑处理更方便,从目前的设置上看来,timing里面体现不出来你用cnt[2]和~cnt[2]的差别

谢谢你的解答,我还有个疑问

虽然我不知道如何去正确的使用invert这个命令。

那么我是否可以通过waveform的选项,将clk8的波形设定下来,使其和clk32有上图的时序图关系

另外,我试着在pt中report_timing,并且比较了clk8加上和不加上invert时的区别,

clk周期为74,clk8为592,clk32为2368.

分析一个时序起点为clk8,终点为clk32的数据路径时发现,

没有-invert选项时,

data_arrival_time 为2072+x;

data_required_time为2368+y;

无invert选项时

data_arrival_time 为1776+x;

data_required_time为2368+y;

从上图的时序来看,应该是没有加invert时数据的检查时刻是正确的,我不太清楚这样的现象是怎么处理,是否可以认为不加invert才是正确的?

clk和clk32啥关系?我前面的表述都是以为clk 和 clk8在做啥事情,没仔细看

下面有个图应该说的比较清楚了

如你所说 用waveform应该会约束的比较清楚。invert的用法最好去man 一下,然后看报出来的时序是不是你想要的 我说的也不一定对

我明白你的意思了,非常感谢你

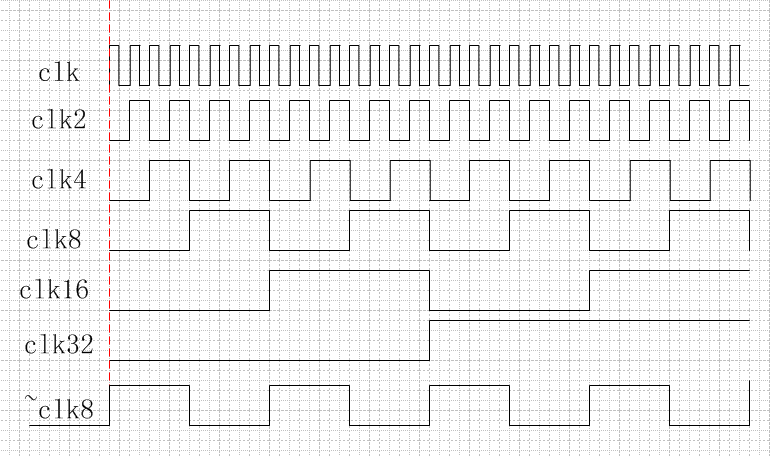

其实可是这么理解,任何一个时钟定义的时候,如果没有加上wave_form,那么默认情况就是0时刻上升沿,half_period时刻下降沿。

因此对于上述的波形情况,因为我的clk8和clk32的波形的上升沿起始时刻是存在一致点的,那么可以理解为clk8和clk32的wave_form的上升沿时刻都是零时刻,然后在各自的半个周期后出现下降沿,因此根据这个情况是不需要加上invert的。

麻烦你看下,我根据下图时序图,通过wave form定义的时钟?其中clk周期为2,其余为分频时钟。

我猜测的可能定义如下,是否正确?

clk wave_form {0,1}

clk2 .... {0,2}

clk4 .... {0,4}

clk8 .... {0,8}

clk16.... {0,16}

clk32 ....{0,32}

~clk8 ...{8,16}

若如此定义create_generate_clock就会发现所有的divide_clock都是0时刻出现上升沿开始的。

如果有一数据通路起始为clk2,结束为clk4,可以预见

data_arrival_time 为 4;

data_require_time为8;

但,实际代码中的clk2为clk_cnt[0],clk4为clk_cnt[1];因此,从代码的角度上讲,

data_arrival_time 为 6

data_require_time为8,

那么是否意味着,这时需要给时钟clk2加一个invert选项?将其反转

waveform定义的不对吧

clk2 .... {0,2}

和你波形不一致啊

至少和你clk的定义方法就是矛盾的

我昨天查了一些generate_clock的资料,对这个分频的终于明白了

上图的那些波形确实不好用wave_form定义

应该用-edges来定义较好,而且使用了edges后各个分频时钟的关系也就定义清楚了