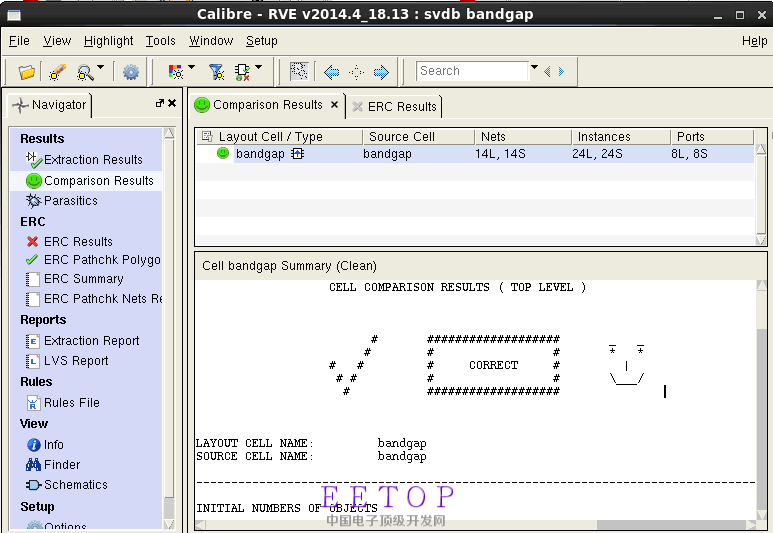

bandgap做LVS验证时遇到这样的问题该如何解决?

时间:10-02

整理:3721RD

点击:

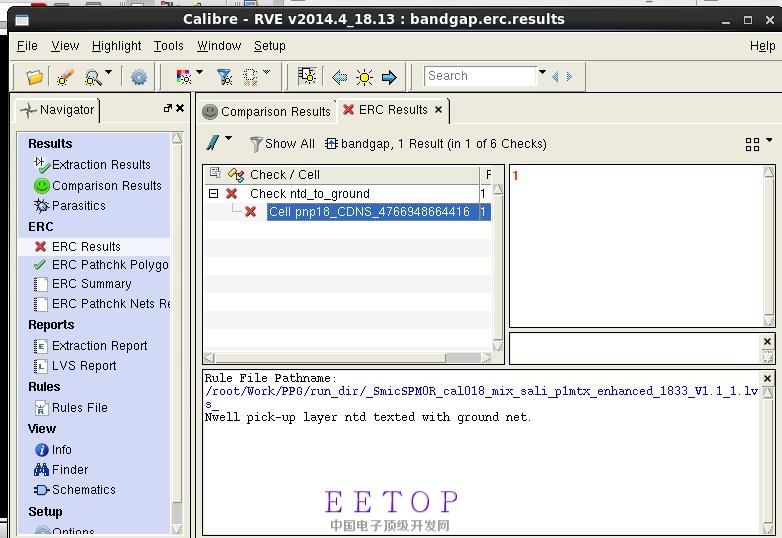

如图,在做LVS验证的时候,comparison过了,然而ERC报错,哪位大神可以解释下这个ERC报错是什么意思?该如何解决?

顶一个,大神来解答一下

这是个ERC提示。因为Nwell接到了地电位,在常见的psub nwell工艺中,这是不太符合常规或者说不太常见的接法,更容易引起本应隔离的PN节正向导通或者触发LU等可靠性问题,所以command file给出提示,指引设计者特别注意此处接法。

感谢回复~检查了整个电路,发现是bjt里的N well接地,请问这个有什么影响么?

没有问题的撒

这个“影响”不是指的你这种具体的电路连接关系,而是这种连接关系的情况下,可能更容易触发一些寄生问题,例如latch up,所以要判断这个“影响”,要结合的是此处layout的布局、以及芯片工作和测试中的应用状态。

最好还是把它清了。

:L:L:L

三极管的erc问题吧,确认一下,应该是没问题的

NWELL接地了,离Pmos远一点,预防latch up

好想知道小编怎么把这个ERC问题清掉的

这个NW接地是follow电路的设计,这个是清不掉,只能评估看有没有风险,能不能waive。推荐的做法是离正电位的NW远一些,有些fab就有rule要求要拉开40um!一般来说,NW接高电位(比如power—VDD),PW(psub)接低电位(比如说ground—VSS),layout这样画一方面是为了符合电路设计,给MOS等器件正确的sub电位,确保lvs不会出错;另一方面,也是为了降低PN结正偏的风险。

建议去找design确认一下