FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序

2.6.1 实例的内容及目标

1.实例的主要内容

本节旨在通过给定的工程实例--"按键开关控制LED"来熟悉Xilinx ISE软件的基本操作、设计、编译及仿真流程。同时使用基于Xilinx FPGA的开发板将该实例进行下载、验证及调试,完成工程设计的硬件实现,熟悉Xilinx FPGA开发板的使用及配置方式。

在本训练中设计软件采用ISE 7.1i,实现功能是利用4个按键开关来控制8个LED灯。具体的显示方案是由4个按键开关控制8个LED灯,根据按键开关按下的不同,会有不同的灯点亮。

在本训练中,将主要讲解下面一些知识点。

Xilinx ISE工程创建及属性设置。 Xilinx ISE源文件设计输入方式。 Xilinx ISE综合。 Xilinx ISE行为仿真。 Xilinx ISE约束设计。 Xilinx ISE布局布线。 Xilinx ISE时序仿真。 Xilinx ISE硬件下载。通过这些知识点,按照下面提供的训练流程,读者可以迅速地掌握使用Xilinx ISE软件进行FPGA开发的方法。

2.实例目标

通过详细的流程讲解,读者应达到下面的目标。

熟悉Xilinx ISE软件的操作环境。 熟悉Xilinx ISE软件开发FPGA的基本流程。 可独立使用Xilinx ISE软件开发新工程。2.6.2 平台简介

本实例基于红色飓风II代Xilinx板,此开发板集成了Xilinx的Spartan3 40万门FPGA及相关的丰富外设资源。

此开发板更加详细的信息、扩展附件及使用方法,可以到红色飓风的官方网站:http://www.fpgadev.com获取更多的信息。

本实例将通过一个简单的实例在这个开发板上对Xilinx的FPGA设计流程做一个全面的介绍,依照此例程的流程便可在该开发板上运行一个FPGA程序。

如图2.65所示为此开发板的一个外观图。

图2.65 红色飓风II代Xilinx板外观图

2.6.3 实例详解

本节同样将使用图解的方式将整个流程一步一步展现给读者,使读者能够轻松掌握ISE的开发流程。

1.工程创建及属性设置

(1)启动Project Navigator。

安装好ISE7.1套件后,可以按照以下的方法打开Project Navigator。

① 在桌面上面双击Xilinx ISE 7.1i的快捷方式图标,如图2.66左图所示。

② 选择"开始"→"所有程序"→"Xilinx ISE 7.1i"→"Project Navigator",打开Project Navigator,如图2.66右图所示。

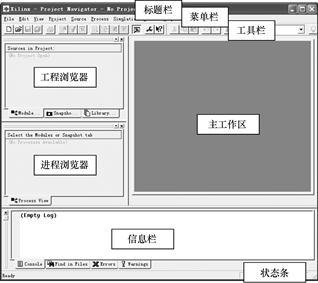

打开后的Project Navigator界面如图2.67所示。可以看到,Project Navigator的界面是一个标准的Windows软件视窗。分别包括标题栏、菜单栏、工具栏、工程浏览器、进度浏览器、主工作区、信息栏、状态栏。

图2.66 ISE的启动

图2.67 Project Navigator主界面

(2)创建一个新的工程。

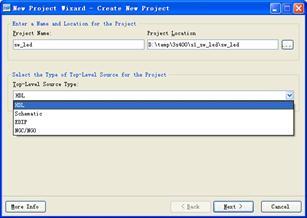

单击"File"→"New Project…",弹出如图2.68所示对话框。

图2.68 新建工程对话框

在这里填写将要创建的工程的名称(Project Name)、路径(Project Location)和工程的顶层模块类型(Top-Level Module Type)。

顶层模块类型我们主要使用前面两种:HDL(Hardware Design Language)硬件设计语言模式和Schematic原理图模式,这里选择HDL。

(3)设置工程属性。

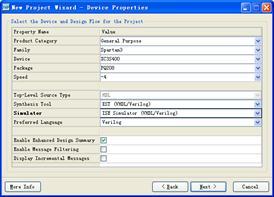

填写好后,单击"Next"按钮,在如图2.69所示的对话框中设置工程的属性。

图2.69 工程属性对话框

在这个对话框可设置的属性定义,如表2.4所示。

表2.4 属性定义

| Device Family | 使用的FPGA的种类 |

| Device | 使用的FPGA的型号 |

| Package | 使用的FPGA的封装 |

| Speed Grade | 使用的FPGA的速度级别 |

| Top-Level Module Type | 顶层模块类型 |

| Synthesis Tool | 综合工具 |

| Simulator | 仿真工具 |

| Generated Simulation Language | 仿真模块语言类型 |

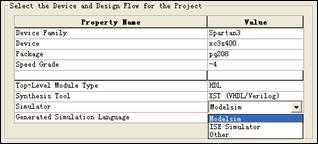

本实例选用的都是ISE自己带的综合工具和仿真工具,这里也可以选择第三方的应用软件,如图2.70和图2.71所示。

图2.70 工程属性对话框选择第三方综合工具

图2.71 工程属性对话框选择第三方仿真工具

ModelSim和Synplify Pro是比较通用的第三方仿真和综合软件。在这里如果我们选择了使用第三方的软件进行综合及仿真的话,在后面执行相应步骤的时候ISE Navigator就会自动寻找并打开相应的软件。

(4)添加设计文件。

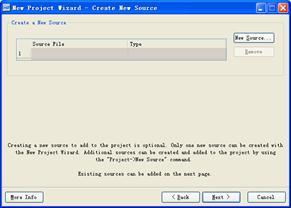

填写好FPGA型号和使用的综合,仿真软件后,单击"Next"按钮打开如图2.72所示的创建源文件对话框。

图2.72 创建源文件对话框

在这个对话框里面,允许

ISE 7 1i FPGA Xilinx FPGA最小系统 相关文章:

- FPGA系列相关图书介绍(06-06)

- Valeo采用LMS SYSNOISE进行超声波停车辅助设备开发(12-19)

- ISE 约束文件 *.ucf的写法(11-21)

- LMS SYSNOISE支持声学传感系统的优化(01-10)

- 基于点判决域的多模盲均衡算法及其FPGA实现(04-26)

- AD7888与S3C2410的SPI接口及Linux下嵌入式驱动的实现(11-06)