FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序

中出现错误,在信息栏中根据错误的提示,修改相关的约束设计,再进行布局布线的实现,直至没有错误为止。

6.布局布线后仿真

在工程浏览器中选择测试文件,双击进度浏览器中"Implement Design"下面的"Simulate Post-Place & Route Model",对工程进行布局布线后仿真,仿真结果如图2.102所示。

图2.102 时序仿真结果

通过与行为仿真结果图2.96对比,可以发现,布局布线后仿真加入了布线的延迟,输出的结果相对于时钟有相应的延迟。在工作区里面单击鼠标右键,在弹出的菜单里面选择"Add Measure"选项,可以通过放大工作区和拖动时间测量游标,读取时间延迟,如图2.103所示。

由上图可以看出,尽管输出相对于时钟存在一定的延时,但输出结果是正确的,符合设计要求,可以进行下载和在线调试了。

图2.103 测量时间延迟

7.下载程序

布局布线完成以后就可以将程序下载到开发板上进行调试。开发板提供两种下载方式:JTAG模式和PROM模式。区别在于JTAG模式是用于在线调试使用的,断电后不保留程序;而PROM模式则是将程序烧写在存储器里面,上电后自动加载。

(1)JTAG模式下载。

如图2.104所示,在进度浏览器中"Generate Programming File"下面可以看到有3个选项,分别是编程文件生成报告、生成编程文件和使用iMPACT配置器件。

在"Generate Programming File"图标上面单击右键,选择"Properties…",弹出如图2.105所示的属性对话框,在其中可以设置下载文件的属性。

图2.104 生成下载文件 图2.105 "General Options"选项卡

在该对话框中有4个选项卡,可以对相应的下载参数进行设置。

"General Options"选项卡里面的"Create Bit File"选项生成用于JTAG模式下载的二进制下载文件。确定选择该项,如图2.105所示。

在"Startup Options"选项卡里面将"FPGA Start-Up Clock"后面的内容改为"JTAG Clock",如图2.106所示,在这里要根据不同的下载模式正确地选择时钟。

在"Readback Options"选项卡里面将"Security"后面的内容置为"Enable Readback an Reconfiguration",如图2.107所示,然后单击"OK"按钮,完成下载的属性设置。

图2.106 "Startup Options"选项卡 图2.107 "Readback Options"选项卡

如图2.108所示,双击进度浏览器里面的"Generate Programming File"图标,ISE将生成供 JTAG模式下载的bit文件。"Generate Programming File"左边的绿色对号说明已经成功生成了下载 文件。

图2.108 生成下载文件

双击"Generate Programming File"下面的"Configure Device(iMPACT)"图标,打开如图2.109所示的iMPACT工具。

图2.109 iMPACT工具

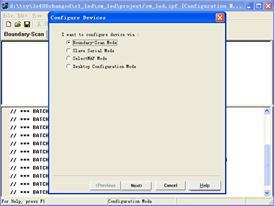

在如图2.109所示的对话框里面选择器件配置的模式,这里选择边界扫描模式"Boundary-Scan Mode",单击"下一步"按钮,如图2.110所示。

图2.110 边界扫描模式选择对话框

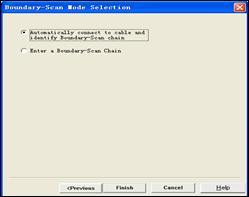

选择自动加载边界扫描链路,单击完成。

由于开发板上面的JTAG和PROM下载是在一条链路上的,所以会弹出如图2.111所示的对话框,单击"确定"按钮就能看见ISE扫描到的开发板上面的下载链,如图2.112所示。

图2.111 边界扫描检测结果对话框

图2.112 ISE扫描下载链结果

其中下面标有xcf02s的图标代表的是PROM,下面标有xc3s400的图标代表FPGA。

双击FPGA图标,在弹出的对话框里面选择刚才生成的二进制下载文件(后缀为.bit)。配置好以后右键单击FPGA图标,在弹出的菜单里面选择"Program…"选项,如图2.113所示。此时将会出现如图2.114所示的下载属性设置对话框。

图2.113 设置配置文件 图2.114 配置设置对话框

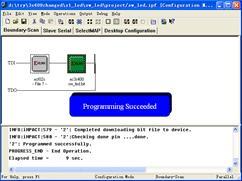

单击"OK"按钮就可以开始下载了。若下载成功将会有如图2.115所示的下载成功提示。

图2.115 JTAG下载成功

(2)PROM模式下载。

PROM模式下载是把程序存在一块存储器里面(开发板上面使用的是Xilinx公司的xcf02s)。当开发板上电的时候,FPGA就自动加载存储器里面的程序。下面是PROM模式下载的具体操作方法。

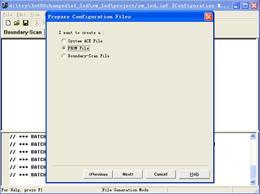

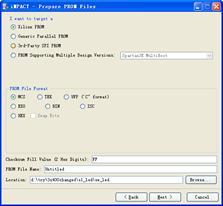

要进行PROM模式下载,首先要生成相应的二进制下载文件,双击进程浏览器中"Generate Programming File"下面的"Generate PROM, ACE, or JTAG File"图标,弹出如图2.116的对话框。

图2.116 生成PROM文件对话框

选择"PROM File"选项,单击"下一步"按钮,打开如图2.117所示的PROM文件配置对话框。

图2.117 PROM文件设置对话框

在该对话框中,选择生成一个Xilinx PROM,后缀选择MCS,文件格式选择FF(十六进制

ISE 7 1i FPGA Xilinx FPGA最小系统 相关文章:

- FPGA系列相关图书介绍(06-06)

- Valeo采用LMS SYSNOISE进行超声波停车辅助设备开发(12-19)

- ISE 约束文件 *.ucf的写法(11-21)

- LMS SYSNOISE支持声学传感系统的优化(01-10)

- 基于点判决域的多模盲均衡算法及其FPGA实现(04-26)

- AD7888与S3C2410的SPI接口及Linux下嵌入式驱动的实现(11-06)