FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序

同样也可以执行"Test Bench"→"Set End of Test Bench…",在弹出的对话框里面修改仿真波形的截止时间,如图2.89所示。

图2.89 截止时间设置对话框

单击"OK"按钮就会发现仿真波形的时间长度由1000ns变成了2000ns。

② 添加仿真激励。

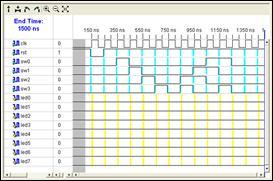

要进行仿真,还需要为仿真添加激励。这里可以通过点击波形图中的蓝色方块来设置输入波形电平的高低,如图2.90所示。

图2.90 设置输入电平

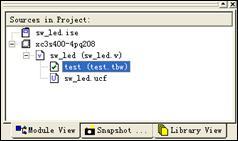

设置好以后一定不要忘记保存波形文件。保存以后就会在工程浏览器的当前工程的子目录下看见刚生成测试的文件,如图2.91所示。

图2.91 保存仿真文件到工程

③ 仿真。

首先在工程浏览器的【Module View】里面选择"test(test.tbw)"。

图2.92 由波形文件生成测试代码

然后在进度浏览器的"Process View"对话框里面双击"View Generated Test Bench As HDL"图标,就能看见ISE根据刚才设置的波形文件自动生成的测试文件,如图2.93所示。

图2.93 生成的测试代码

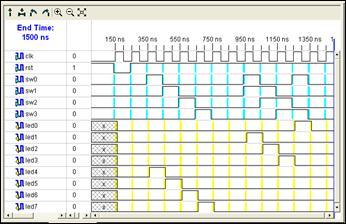

在进度浏览器中双击【Generate Expected Simulation Result】,弹出两个对话框,都选择是(Y),将看见生成的预期输出波形,如图2.94所示。

图2.94 预期仿真波形

在进度浏览器中双击"Add Test Bench to Project",将测试波形添加到工程里面。将会看到工程浏览器中test文件的图标由 变成

变成 。

。

如图2.95所示,在进度浏览器中双击"Simulate Behavioral Model"将对工程进行行为仿真,仿真结果如图2.96所示。

图2.95 运行功能仿真

图2.96 功能仿真结果

从图中可以看出功能仿真结果符合设计要求,可以继续进行下面的设计。如果此处仿真发现设计功能不符合要求,则要对原代码进行修改,直到仿真结果符合设计要求为止。

4.约束设计

在源程序输入完成以后,就可以设置约束,规划布局布线了。

约束有很多种:时序约束(Timing Constrains)、管脚约束(Assign Package Pins)以及面积约束(Area Const- raints)等。

如图2.97所示是ISE进度浏览器中包含的用户约束的选项。

图2.97 设置约束

(1)时序约束。

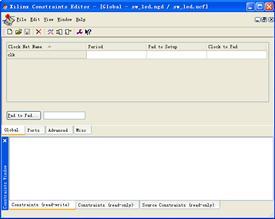

时需约束主要约束设计的时序和时钟频率,双击图2.97中的"Create Timing Constraints"图标,ISE将打开约束编辑器,如图2.98所示。

图2.98 时序约束界面

在约束编辑器里面有4个复选页,定义如表2.5所示。

表2.5 属性定义

| 属 性 | 定 义 |

| Global | 用于附加全局约束,包括周期约束,输入延迟约束和输出延迟约束 |

| Ports | 附加端口约束,可以对每一个端口进行单独设置,包括物理位置、输入延迟和输出延迟。同时,也可以设置分组,进行分组约束 |

| Advanced | 附加分组约束(TNM/TNM_NET/TIMEGRP)和时序约束(FROM_TO/TIG O/OFFSET)等 |

| Misc | 附加专用约束,包括电压、初始值等 |

| | 注意 | 附加约束的原则是先加全局约束后加分组约束。 |

在本实例中只做简单的时钟约束。在clk的period中输入:20ns HIGH 50%,即设置时钟的周期和占空比。设置后保存,完成时序约束。

(2)管脚约束。

管脚约束即约束工程设计源文件与选定器件对应的输入/输出管脚属性。双击图2.97中的"Assign Package Pins"图标,ISE将打开PACE工具,如图2.99所示。

通过图2.99的"Design Object List"对话框里面的Loc列,可以为设计添加输入/输出管脚,添加形式为"Pxxx"或者"pxxx"。其中P/p代表Pin,xxx是数值。

(3)面积约束。

面积约束目的在于规划FPGA里面的逻辑使用大小。双击图2.97中的"Create Area Constraints"图标,ISE同样打开PACE工具,面积约束和管脚约束用的是一个界面。在面积约束里面我们可以对设计使用的资源面积加以规划,控制使用资源在FPGA里面的位置。

这里只使用到管脚约束,按照按键和LED灯与FPGA的连接,输入管脚分配,然后保存分配。在保存选项中,选择"XST Optional",如图2.100所示,关闭对话框,完成约束设计。

图2.99 管脚约束工具PACE

图2.100 保存管脚约束结果

5.布局布线

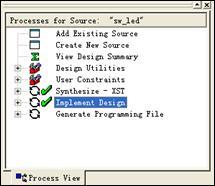

设置好了各种约束以后就可以进行布局和布线了。双击进度浏览器中的"Implement Design",开始进行布局布线实现。与综合相同,如果在"Implement Design"的右边出现绿色的对号,说明已经完成布局布线,没有发现错误,如图2.101所示。

图2.101 运行布局布线

如果实现过程

ISE 7 1i FPGA Xilinx FPGA最小系统 相关文章:

- FPGA系列相关图书介绍(06-06)

- Valeo采用LMS SYSNOISE进行超声波停车辅助设备开发(12-19)

- ISE 约束文件 *.ucf的写法(11-21)

- LMS SYSNOISE支持声学传感系统的优化(01-10)

- 基于点判决域的多模盲均衡算法及其FPGA实现(04-26)

- AD7888与S3C2410的SPI接口及Linux下嵌入式驱动的实现(11-06)