基于点判决域的多模盲均衡算法及其FPGA实现

摘 要: 恒模算法无法克服信号的相位失真问题,且稳态误差大;修正恒模算法可以恢复信号相位,但均衡器收敛后,稳态误差依然很大。针对这一问题,提出一种基于点域判决的多模盲均衡算法,算法利用信号的判决值,在不增加设备复杂性的前提下,可以降低均衡器的稳态误差。给出了多模算法的FPGA设计方案,基于Xilinx公司的ISE设计平台,在Modelsim中进行了时序仿真分析,并和MATLAB仿真进行了比较。实验结果表明盲均衡器可以克服信号的幅度和相位失真,并且具有稳态误差低的优势。

关键词: 恒模算法;修正恒模算法;多模算法;FPGA实现

盲均衡由于无需使用训练序列,有效地提高了频带利用率,因而在高速卫星通信系统中得到了广泛应用。在各种盲均衡算法中,恒模算法CMA(Constant Modulus Algorithm)[1]因其实现简单、性能稳定而备受重视。CMA只利用了信号的幅度特性,无法克服相位失真问题,文献[2]提出的修正恒模算法MCMA(Modified Constant Modulus Algorithm)可以恢复信号相位,但稳态误差性能改善有限。本文在上述文献的基础上,提出一种基于点判决域划分的多模盲均衡算法。

随着FPGA器件规模、处理速度的发展,它在数字信号处理领域的应用日渐广泛,文献[3,4]讨论了FPGA在数字调制和载波跟踪方面的应用。本文选用Xilinx公司的ISE设计平台,对多模盲均衡算法进行FPGA的设计与实现,使其可以应用在实际的卫星通信系统中。

均衡器权系数向量的更新方程采取式(2)的随机梯度下降算法。

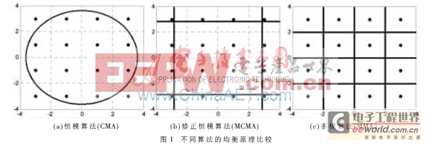

图1表示三种算法的均衡原理。图1(a)是CMA的工作原理,CMA使均衡器的输出向图中固定半径的圆逼近,只考虑了信号的幅度信息,故均衡器收敛后稳态误差大;图1(b)是MCMA的工作原理,MCMA使输出信号的实部左右两条线靠拢,虚部向上下两条线逼近,该算法考虑了信号的相位信息,因此可以克服信道特性以及载波偏移引起的相位失真;图1(c)是MMA的工作原理,均衡器使信道输出向最为接近的星座点逼近,因此均衡器收敛后,可以获得最小的稳态误差。

2 多模算法的FPGA设计

选用Xilinx公司的Spartan 3E系列产品中的XC3-S1600E器件,运用ISE9.1i的集成开发环境进行综合和实现,联合第三方软件modelsim进行仿真,使用VHDL硬件描述语言实现多模盲均衡器。

2.1 均衡器结构设计及功能描述

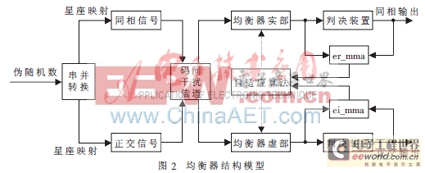

多模盲均衡器结构见图2。

(1)信源模块:利用线性反馈移位寄存器产生伪随机序列,序列的特征多项式采用f(x)=1+x3+x7。经过串/并变换后,将每一路的4个比特映射为对应的电平序列,形成16QAM的同相和正交信号。

(2)滤波器模块:滤波器模块包括信道滤波器和均衡器,信道冲激响应和均衡器权系数均采用FIR滤波器结构。为了节省硬件资源,FIR滤波器采用串行结构实现。信道滤波器采用系数固定的FIR滤波器,均衡器采用系数可调的FIR滤波器。

(3)判决模块:判决装置对均衡器的输出进行决策,利用最小距离准则,在16QAM星座图的字符集中找到与均衡器输出最接近的点作为当前信号点的判决值。

(4)误差计算及系数更新模块:迭代误差的计算依据式(12)进行,系数的更新则采用式(2)的最陡下降法。

2.2 数据格式及截位

在FPGA中,信号和数字用二进制定点有符号数表示,定点值采用补码表示法[5]。算法中涉及的信号和变量的数据格式如表1所示。

算法执行过程中,信源信号s(k)、信道系数h(k)、信道输出x(k)、均衡器输出y(k)、判决输出d(k)均用8 bit字长表示;误差信号e(k)、均衡器系数w(k)、步长因子则用16 bit字长表示;均方误差mse(k)用32 bit字长表示。

在有限字长的情况下,加法运算和乘法运算会增加操作数的位宽,为了节约硬件资源,对乘法运算后的数据进行有效截断。由于信号能量、信道系数均进行了归一化,运算过程中没有出现溢出现象,保证了运算结果的准确性。

3 MATLAB仿真及FPGA实现

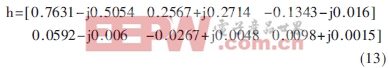

针对16QAM系统对算法进行性能仿真和分析。均衡器的抽头数为7,中心抽头权值初始化为1,其余抽头权值初始化为零。卫星信道的信道参数为:幅频响应满足奈奎斯特升余弦特性,群时延失真为2.25个码元宽度,信道长度为6,FIR系数为:

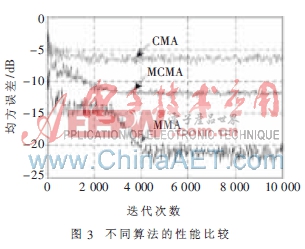

图3示出三种算法收敛速度比较,信道信噪比为25 dB,曲线通过100次独立的蒙特卡洛夫仿真获得。从图中可见,CMA的稳态误差为-6 dB左右,MCMA的稳态误差为-12 dB左右,而多模算法的稳态误差达到了-21 dB,相对于前两种算法,其优势非常明显。三种算法的迭代速度均为4 000个码元左右。

图4(a)和4(b)分别由Matlab仿真和modelsim仿真得到,FPGA的时钟周期为50 MHz。图中显示的是多模盲均衡算法前100个码元均方误差的迭代

FPGA ISE 恒模算法 修正恒模算法 多模算法 Xilinx 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)