在采用FPGA设计DSP系统中仿真的重要性

在电信领域,一直采用现场可编程门阵列(FPGA)做为预/后处理器或者协处理器。语音电信应用中的数字信号处理(DSP)要求输入数据为正常语音速率,具有严格的时序约束,要求能在连续的输入数据采样间完成计算。采用DSP处理器之后,在整个计算中可以执行数万条指令。但是,无线通信中,一个DSP处理器无法实时实现中频(IF)和基带调制解调器中的高速算法。利用某些DSP处理器的多个处理单元可以克服指令带宽限制。然而,创建专用的流水线代码以真正发挥这种并行(同时执行)的优势需要手工优化汇编语言例程。

对这类代码进行维护、重用和实现会产生很多问题,成本比较高。而且,实际的并行能力也相对较弱。用于实现高带宽计算的比较好的替代方案是采用FPGA做为预/后处理器或者协处理器,将重复算法和算法中对速率要求严格的部分集成到FPGA中。采用FPGA和自动设计软件后,工程师能够采用单纯用DSP不可能实现的方式来优化系统性能。

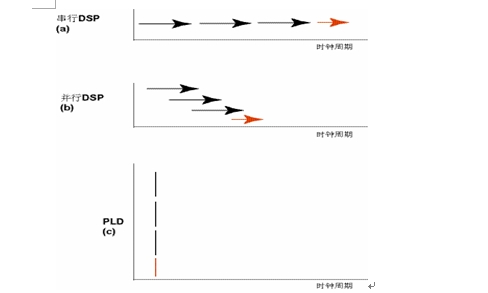

图1显示了FPGA的速率优势。由于是并行算法,因此,计算吞吐量和时钟周期数之比非常高。现在单个FPGA能够实现几百个千兆MAC区。为了发挥这种性能潜力,可以利用Altera DSP Builder模块组构成的Simulink结构图来建立一个系统。DSP Builder的好处在于可通过采用标准信号处理模块,在PLD中建立一个高速信号处理系统,而不必通过HDL编程。

设计人员可以利用DSP Builder中的模块,为Simulink中的以采样时间建模的系统生成硬件实现。具体工具包括比特和周期精度级的Simulink模块,包含算法和存储功能等基本操作。Altera DSP IP库支持的复杂功能和子系统,也可以采用提供的DSP Builder模块组来集成。

FPGA中的DSP系统设计需要高级算法和后端HDL开发工具,将自动生成的HDL综合到硬件中。采用这两种集成工具,设计人员不需要成为VHDL或者Verilog程序员。这些程序包是自动系统生成工具,在其中对硬件系统组件进行定义、互联、仿真和验证,不需要进行下层的HDL的编程。采用真正的"指向然后点击"设计方法,完全在PC中将系统结构生成一个完整的系统,对其进行仿真和验证,并下载到FPGA中。

图1.一个算法的串行和并行实现对比

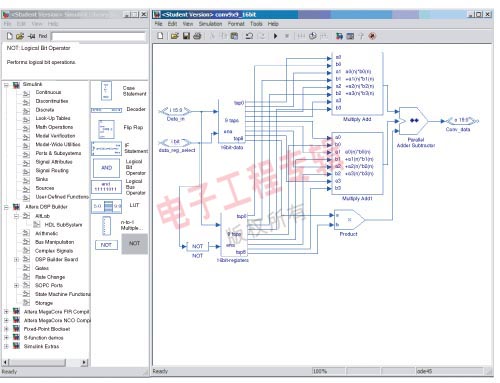

DSP Builder使用 MathWorks公司的MATLAB工具和Simulink环境来生成信号处理系统。这一工具结合了MATLAB/Simulink的算法开发、仿真、验证功能以及FPGA设计软件的硬件综合和仿真功能。DSP Builder集成到Simulink中,系统、算法和硬件设计人员利用这一工具可以共享使用"拖放"结构的开发平台。从大菜单选项中选择DSP Builder模块组的组件,将其放置到Simulink工作空间中,用鼠标点击把它们连接起来。通过下拉菜单来控制指定组件的参数。

图2. 一个互相关的DSP Builder结构图

在做出决定使用FPGA处理来实现项目时,主要设计任务是将设计划分为多个任务,在协处理器、DSP处理器或者其他系统微处理器(主处理器)中实现。在某些情况下,使用软核处理器后,能够在一个FPGA中实现整个系统,从而可以从硬件设计中省去主处理器。进行任务划分时,解决问题最简单、最直接的方法是将问题分成两个独立但又相关的部分:计算算法本身和算法的硬件控制。

对设计进行划分时,设计人员一般会发现,算法中有的部分很显然应该放到FPGA中,而有的则取决于很多系统问题,例如控制代码的内容等。进行这种判断的一个好方法是开发代码的高级语言(例如C/C++或MATLAB)模型。

与复杂系统的设计判断一样,将全部或者部分算法移植到FPGA协处理器中取决于很多因素,需要对设计中硬件和软件组件的性能需求、容量、复杂度和灵活性进行分析。例如,对于目前能在低成本DSP处理器中以足够速度运行的一个简单算法,将其移植到PLD中运行就不一定合适,除非设计目的是进一步提高硬件集成度,缩小PCB面积。然而,如果您的系统性能很高,已经把DSP处理器的性能发挥到极限,但仍然要求系统具有更新的灵活度,那么FPGA协处理器将是唯一的可行方案。

图3. DSP Builder设计流程

Altera设计软件(Quartus II 软件、DSP Builder和用于集成控制面组件的SOPC Builder系统集成工具

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)

- RS编译码的一种硬件解决方案 (06-21)