FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序

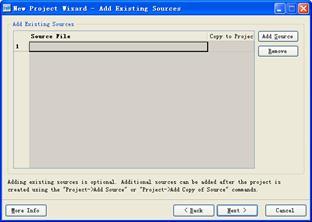

用户为即将建立的工程创建一个新的源文件,并且这里只可以创建一个源文件。其他的要在工程建立以后创建,也可以在创建工程以后再建立所有的源文件。直接单击"Next"按钮,进入如图2.73所示的添加源文件对话框。

在这个对话框里面为即将建立的工程添加已经存在的源文件。如果没有现成的源文件,直接单击"Next"按钮,完成新工程的创建。

(5)完成工程创建。

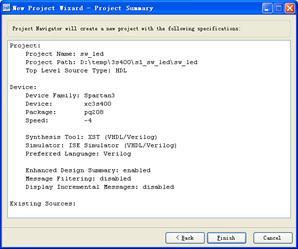

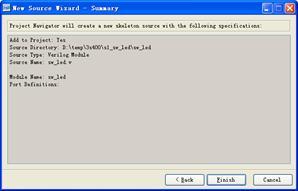

在如图2.74所示的新工程信息对话框中,列出了新建工程的相关参数及属性。

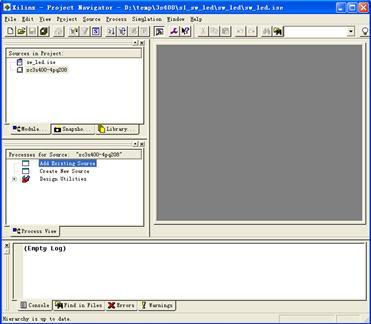

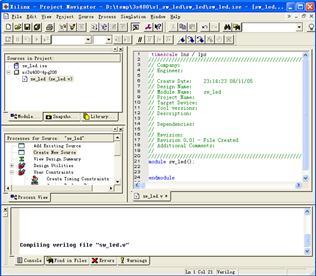

在这个对话框里面显示将要创建的工程的全部信息,确认无误后单击"Finish"按钮,Project Navigator将自动创建一个名为sw_led的工程。如图2.75所示是新工程的界面。

图2.73 添加源文件对话框

图2.74 工程信息对话框

图2.75 工程创建后的界面

2.设计输入

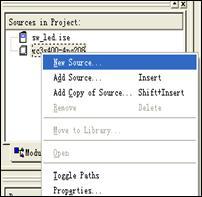

创建好工程以后就要为工程添加源文件了,具体方法如下。

为工程添加源文件有两种方式,可以双击"Process View"对话框里面的"Create New Source",也可以在"Module View"对话框里面的"xc3s400-4pq208"图标上面单击鼠标右键,选择"New Source…"选项,如图2.76所示。

图2.76 添加源文件的两种方式

选择"New Source",弹出如图2.77所示的新建源文件对话框。

图2.77 新建资源对话框

在右面的"File Name"栏里面填写要生成的源文件的名字,在"Location"栏填写源文件保存的路径,一般位于工程文件夹里面,没有特殊需要不必更改。另外一定要选择"Add to project"选项,然后在左边的一排图标里面选择源文件的类型后单击"Next"按钮,进入如图2.78所示的Verilog源定义对话框。

可以在上面的对话框里面输入源文件的模块名称和管脚定义,也可以先不输入,后面写程序的时候自己输入。单击"Next"按钮,完成源文件的创建,在如图2.79所示的对话框中列出了新建源文件的一些信息。

确认信息无误后,单击"Finish"按钮,ISE将生成名为sw_led.v的源文件,如图2.80所示。

图2.78 新建Verilog文件设置对话框

图2.79 新建源文件信息对话框

图2.80 添加新资源后工程界面

用户可以在工作区中开始进行设计的输入,也可参考实例代码中的例程,将代码直接复制到新建的Verilog文件下。输入好程序以后,保存源文件,完成设计的输入。

3.综合及仿真

(1)综合。

在"Process View"对话框里面双击"Synthesize – XST",开始进行工程的综合,如图2.81所示。

综合主要检查源文件程序里面的语法错误(Check Syntax),双击"View Synthesis Report"可以观察综合的结果报告,如图2.82所示。

图2.82 综合报告

如果在这步发现源程序的设计语言有语法毛病,就会弹出Error警告。这样就可以根据报错的位置,在源程序里面查找错误位置,修改好以后重新进行综合,直至无错误为止。

(2)综合后仿真。

这里的仿真是综合后的仿真,也可以称为功能仿真。仿真时并不考虑工程的约束条件及器件的资源使用状况,因此不会产生仿真延迟。这里使用的是ISE自带的仿真工具进行综合后仿真。下面是仿真的步骤。

① 产生仿真文件。

如图2.76的方式,在"New Source"对话框里面选择创建Test Bench Wavefrom文件,如图2.83所示。

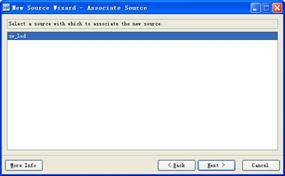

单击"Next"按钮,在如图2.84所示对话框中为Test Bench指定源文件。如图所示在源文件对话框中只有一个文件,这是因为我们只为工程添加了一个设计文件。如果我们为工程添加了几个设计文件,在这个对话框中,将出现多个源文件。此时用户可以选择需要进行仿真的源文件即可。

图2.83 新建Test Bench对话框

在本训练中,将要进行仿真的源文件是sw_led,如图2.84所示。单击"Next"按钮完成仿真文件的产生,如图2.85所示。

图2.84 为Test Bench指定源文件

图2.85 Test Bench信息对话框

单击"完成"按钮,ISE将创建名为test.tbw的仿真文件,同时弹出如图2.86所示的对话框。在该对话框中,用户可以对仿真的时间参数进行设置。

在这个对话框中,包括时钟信息、时钟时间信息、全局信号、仿真时间等多个参数都可以进行设置。按照仿真需求修改好时间参数以后,单击"OK"按钮就能在ISE的工作区里面看见新建的波形文件了,如图2.87所示。

在波形文件里面,clk是时钟信号,在前面的时间参数设计里面已经设置好了。用户若需要对时钟进行更改,可选择执行"Test Bench"→"Rescale Timing…"命令,弹出修改时间参数的对话框,如图2.88所示。

图2.86 仿真时间参数设置对话框

图2.87 时钟波形 图2.88 修改时间参数对话框

同样也可以执行"Test

ISE 7 1i FPGA Xilinx FPGA最小系统 相关文章:

- FPGA系列相关图书介绍(06-06)

- Valeo采用LMS SYSNOISE进行超声波停车辅助设备开发(12-19)

- ISE 约束文件 *.ucf的写法(11-21)

- LMS SYSNOISE支持声学传感系统的优化(01-10)

- 基于点判决域的多模盲均衡算法及其FPGA实现(04-26)

- AD7888与S3C2410的SPI接口及Linux下嵌入式驱动的实现(11-06)