基于NETFPGA的可重构科学计算平台

D:/scicoshdl_nv/scicos-hdl)

2. open /scilab-5.1/modules/scicos/etc/scicos.start

before (//end // if %scicos)

please add the following sentence:

exec(D:/bak/scicoshdl_nv/scicos-hdl/ScicosHDL_start.sce);

3. Run Scilab/Scicos, you can use Scicos-HDL now.

Scicos-HDL is a free software.

Under Scilab licence.

Scicos-HDL Copyright (c) 2004-2010

ZhangDongKangCai (NXU, LIAMA,SCILAB)

scicoshdl@gmail.com

4. all examples :/scicos-hdl/example

5. Contact: scicoshdl@gmail.com

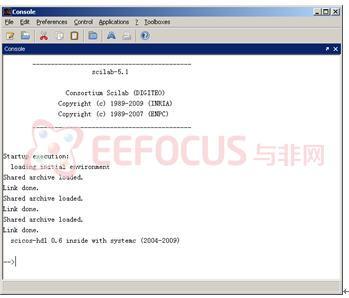

安装完成之后,启动Scilab5.1 , 可以看到Scilab加载的时候,Scicos-HDL已经启动。

Scicos-HDL安装后Scilab启动界面

3.3.4安装SIVP

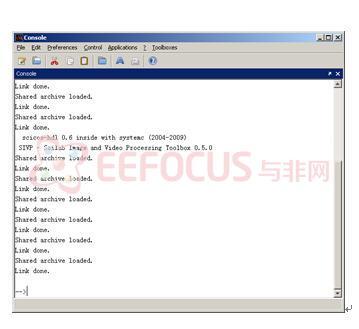

Scilab图像读取等工作我们使用了SIVP作为工具,因此需要安装 SIVP (http://sivp.sourceforge.net/ 下载 )

启动Scilab后,点击Toolboxes菜单的SIVP菜单,启动SIVP.

3.3.5启动Scicos

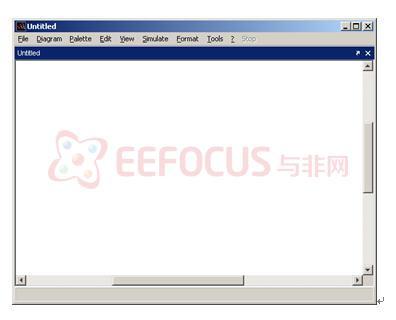

在Scilab中输入 scicos 命令, 即可启动Scicos

启动scicos

Scicos启动后界面如下:

Scicos界面

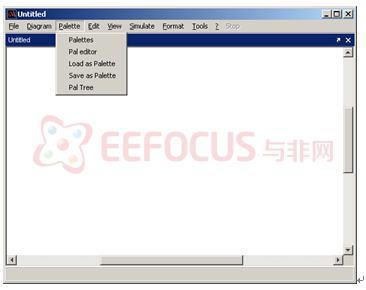

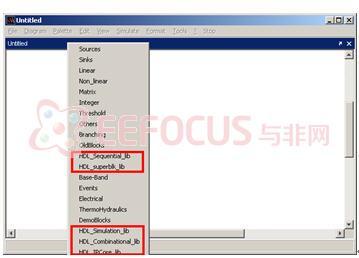

点击Palette菜单的Palette选项

Scicos元件菜单

点击以后可以看到Scicos-HDL的各个库文件已经安装

Scicos元件菜单

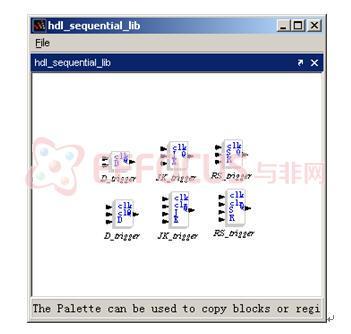

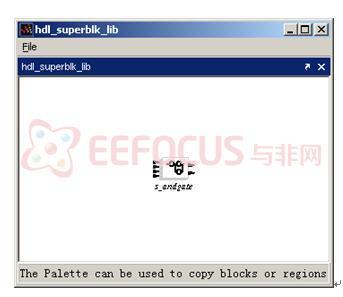

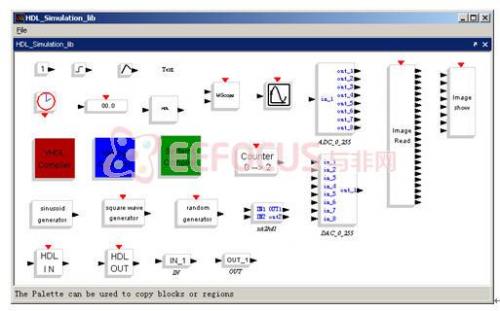

3.3.6Scicos-HDL

时序逻辑元件库

超级元件库

虚拟仪器库

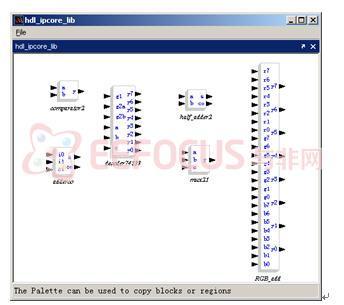

IP 元件库

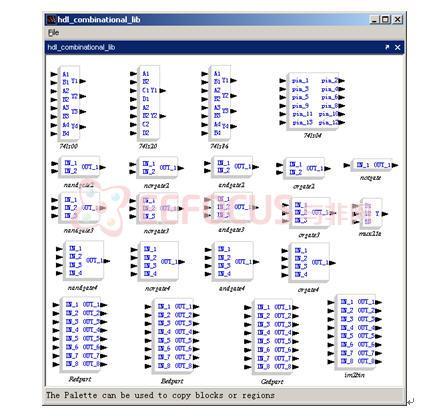

组合逻辑元件库

3.3.7打开实验工程

使用Scicos 打开 设计工程

打开实验工程

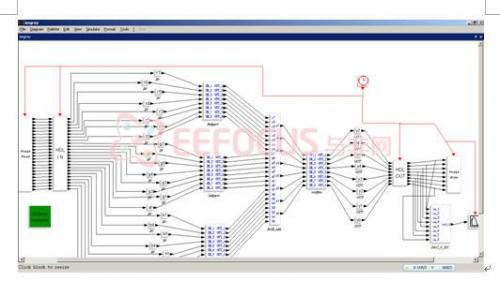

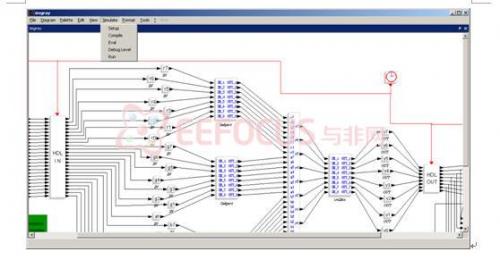

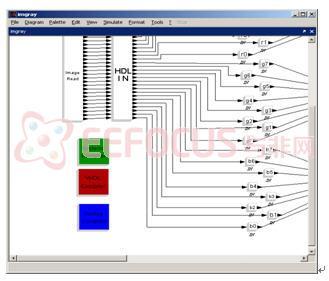

图像处理工程

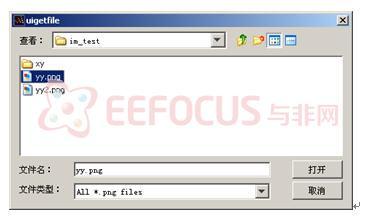

加载图片

加载的图片显示

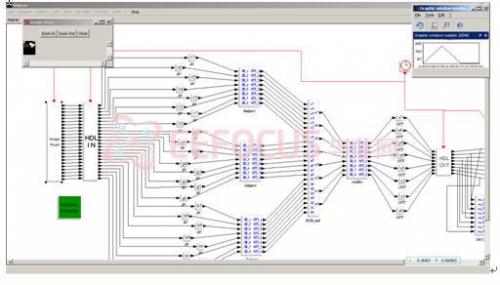

点击simulate菜单中的RUN选项

处理过程开始

处理完成的结果

代码输出

使用VHDL、Verilog、SystemC编译器对设计好的代码进行输出。

输出的VHDL代码

输出的Verilog代码

输出的SystemC代码 (带一个VC++ 2008的工程文件做调试用,Scicos-HDL系统内置 BCC5.5)

硬件连接图

NETFPGA直接通过JTAG接口与计算机相连

NETFPGA与Scicos-HDL协同运算部分,部分完成,本项目未完全完成,尚需继续努力。(略)

3.4提交的内容

本项目的软件部分和设计部分完成,硬件部分部分完成。

提交的内容:

Scicos-HDL 0.7

实验设计和测试文件 imgray.cos

实验输出的SystemC 、VHDL、Verilog代码

FPGA代码模板

- 动态可重构系统的通信结构研究(06-06)

- 采用FPGA部分动态可重构方法的信号解调系统设计(06-05)

- 基于FPGA的动态局部可重构实现方法(06-04)

- 手持移动终端的可重构天线设计(12-20)

- 可编程模拟器件在接收机动态可重构结构应用(03-31)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)