基于NETFPGA的可重构科学计算平台

rtan IIE 30万门的FPGA,系统时钟为50MHz。实际运行完全满足设计要求。

H TTP 协议及其实现

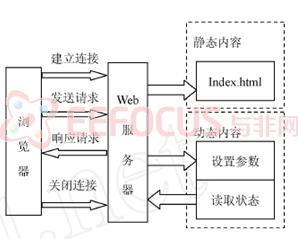

嵌入式Web 服务器技术的核心是HTTP (超文本传送协议) 引擎。HTTP 是WWW 上的协议。HTTP 协议使Web 服务器和浏览器可以通过Web 交换数据。他是一种请求/ 响应协议,即服务器等待并响应客户方请求。当用户要浏览服务器上的一个网页时,一个HTTP 请求就会从用户的浏览器发到HTTP 服务器。服务器响应这个请求, 把指定的网页传送回来, 用户才看到了网页。

HTTP协议不维护与客户方的连接,他使用可靠的TCP连接,通常采用TCP 的80 端口。客户/ 服务器传输过程可分为4 个基本步骤:浏览器与服务器建立连接;浏览器向服务器请求文档;服务器响应浏览器请求;断开连接。服务器程序开始运行时,主进程就创建一个套接字,

并与主机地址绑定到一起,随后置为被动监听状态,等待客户端连接请求的到来。一旦接收一个连接,就返回一个新的套接字描述符,主程序则开辟一个新的子程序来处理这个新的连接。这样系统可以同时

接收多个客户端的请求。首先创建套接字,将套接字与本地地址和端口绑定,并设置套接字处于监听状态。Web 服务器在接收一个连接请求后,读取用户的请求,根据用户的请求进行相应的处理。当请求位静态文本时,文档直接提交输出,当请求位动态文本时,请求模块自动调用脚本引擎,将脚本替换位现场数据,再提交输出,当请求为带参数的执行命令时,请求解析器调用命令执行模块分析命令并控制监控前端。

Http 设计模型

CPU 本身是以软核的方式实现,其功能可根据需要进行定制,非常灵活。EDK 不但在硬件设计上提供了支持,在软件上也为设计者提供了较好的支持,提供了现成的网络协议栈。加上EDK提供的集成开发环境使得软件开发更加便利。采用这种方式的控制系统具有控制分散、开放性好、使用简单、稳定性好等优点,而且可以通过浏览器进行远程多点监控和远程支持,是未来控制系统发展的一个趋势。

2.3.6IP核封装

设计使用输入GPIO 32位,输出GPIO 32位。

2.3.7设计过程

Software:Xilinx ISE Design Suite 10.1 SP3

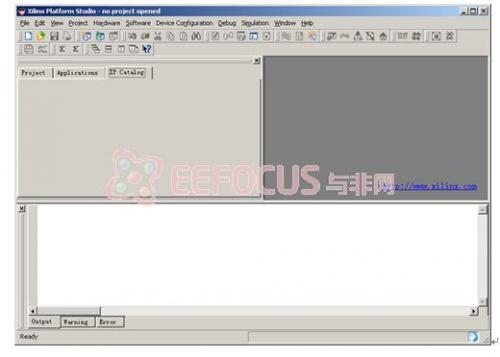

ISE主界面

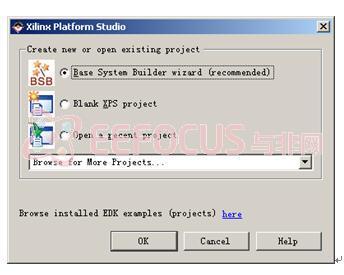

新建一个工程

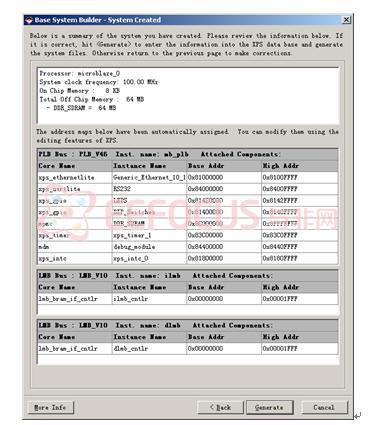

选择FPGA信号和嵌入式处理器型号

选择时钟频率和调试方式

添加 ETHERNET模块、GPIO模块和内存模块

添加系统时钟

设置调试方式和系统测试

系统设置清单

设置完成并保存

设置完成后的工程

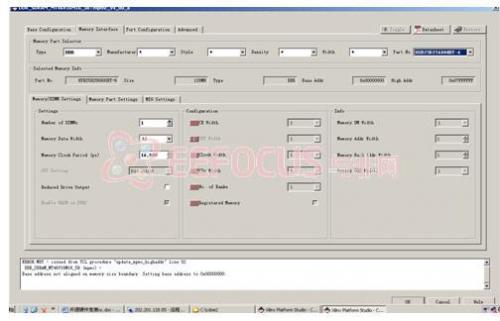

定义内存型号

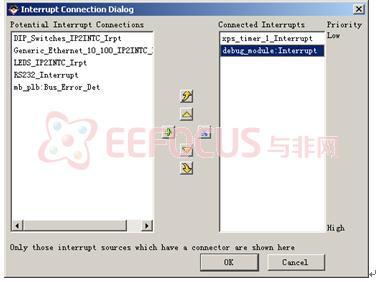

定义系统中断

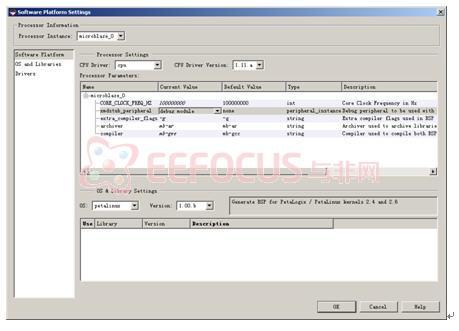

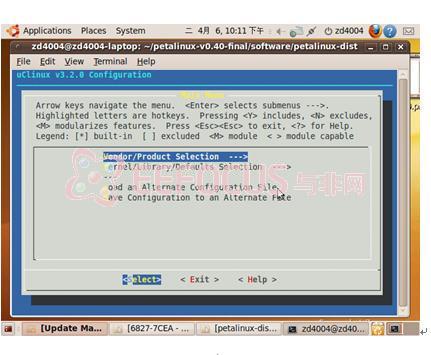

选择操作系统 petalinux

2.3.8设计截图

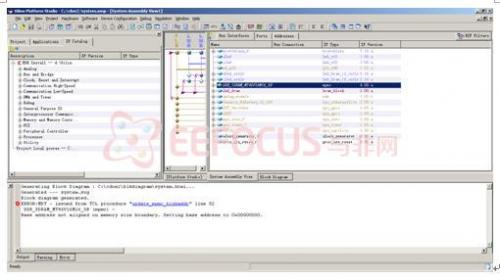

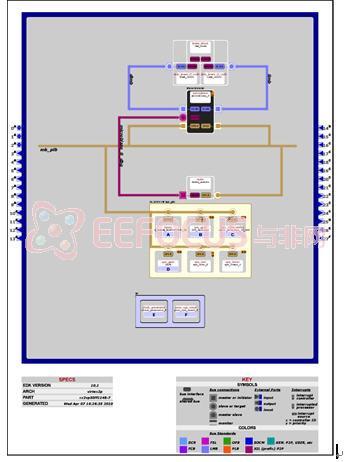

设计完成之后的系统设计图

2.3.9编译代码

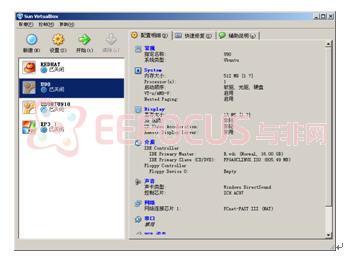

对于嵌入式LINUX系统代码的编译,本项目采用虚拟机的方式在Ubuntu下完成。

虚拟机采用开源的 Sun VirtulBox

启动Ubuntu

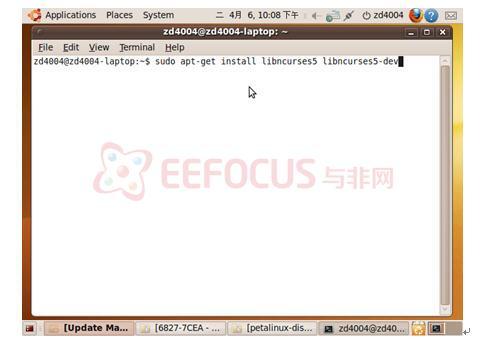

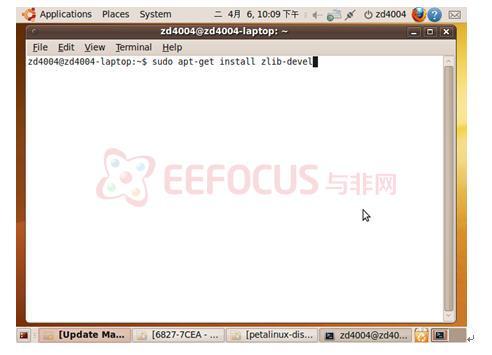

安装缺少的库

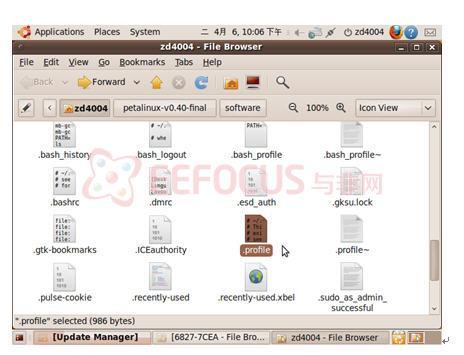

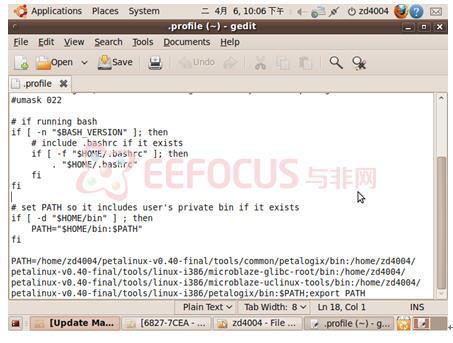

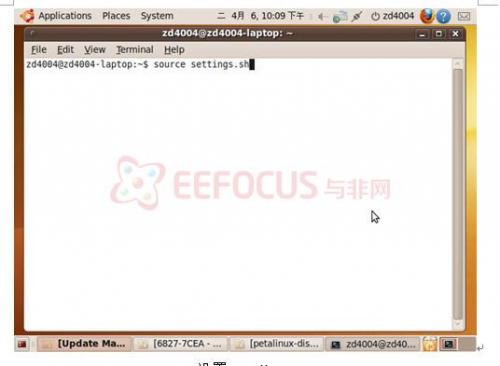

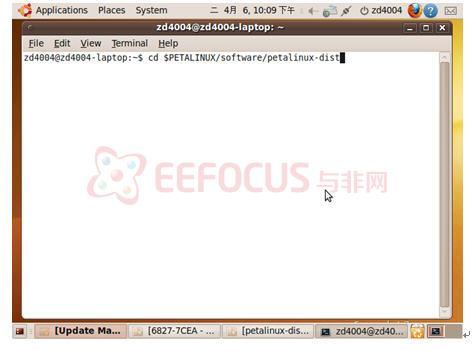

设置环境变量

设置环境变量

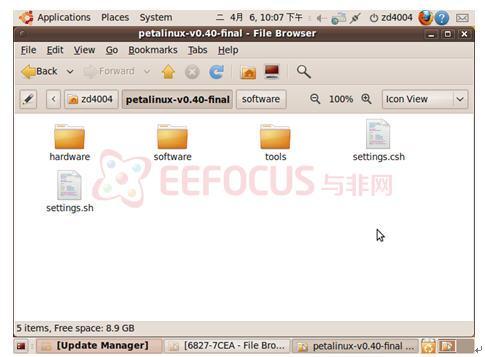

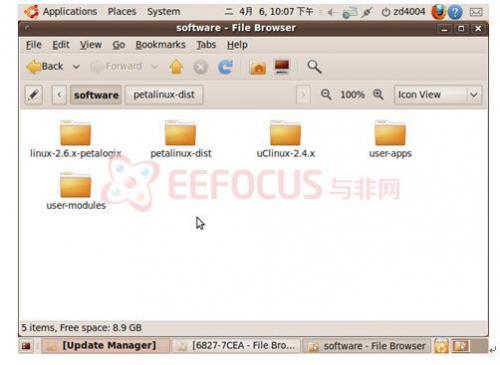

Petalinux文件

Petalinux文件

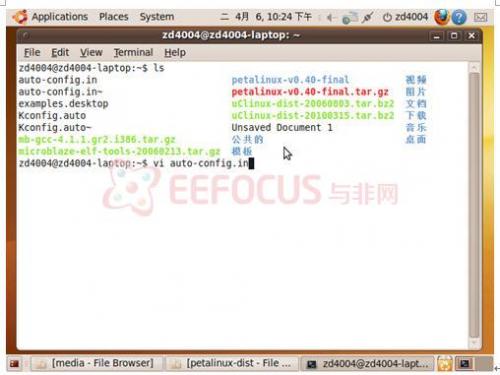

设置Petalinux

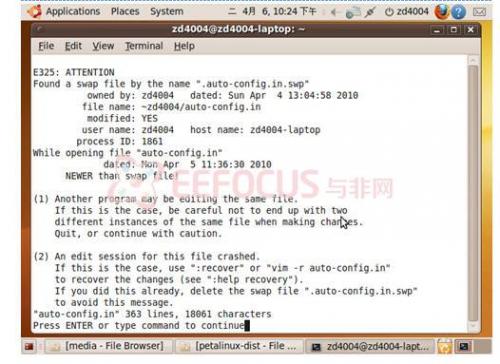

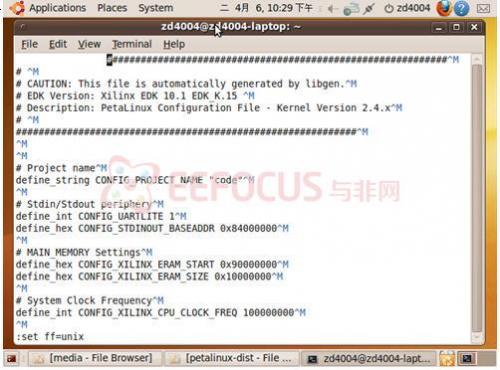

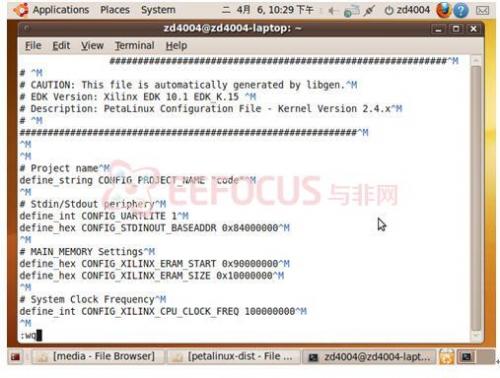

转换autoconfig.in的格式。输入命令:

>vi autoconfig.in

将出现vi的编辑界面,在vi的命令行模式输入以下命令:

>:set ff=unix

然后保存退出。输入命令:

>:wq

这样,就完成了autoconfig.in的导入工作。

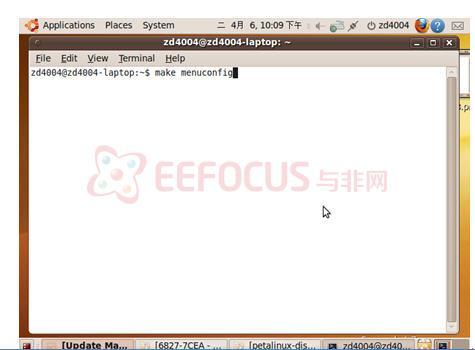

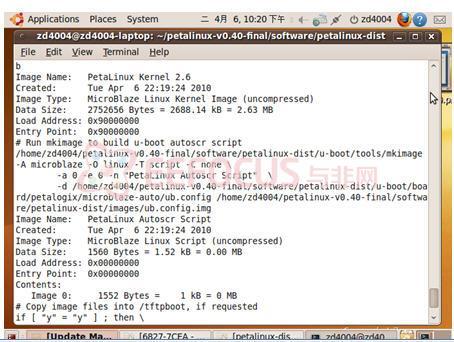

编译Petalinux

开始编译

编译完成

3实验与分析

3.1实验设计

3.1.1实验题目

24位彩色图像的2值化处理

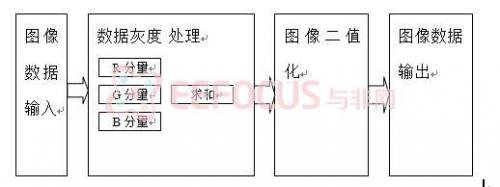

3.1.2实现结构

根据RGB图像灰度公式 :

Gray =0.299*R+0.587*G+0.114*B (公式1)

Gray = (R^2.2 * 0.2973 + G^2.2 * 0.6274 + B^2.2 *0.0753)^(1/2.2) (公式2)

本实验中使用 公式1 进行计算

灰度图像二值化方法:

阈值法二值化

实验中采用一个根据参数可调整的设计,以体现本系统在算法可重构方面的优点。

实验原理图

3.2模块分析

本节对于实验中所使用的各个模块进行分析。

3.2.1输入模块

负责图像的输入:

图像读取模块

3.2.2数值计算模块

负责处理图像数据的灰度变化和二值化计算。

3.2.2.1R分量元件

计算: 0.299*R 采用ScilabCode组合元件模式实现

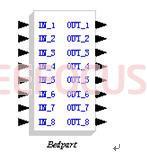

引脚设置

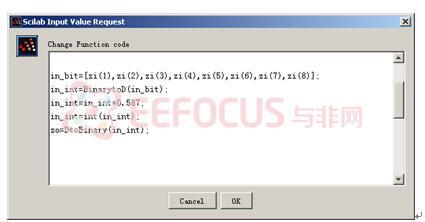

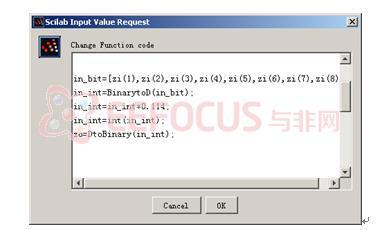

功能设置

3.2.2.2G分量元件

计算 0.587*G采用ScilabCode组合元件模式实现

界面设置

功能设置

3.2.2.3B分量计算元件

计算 0.114*B采用ScilabCode组合元件模式实现

引脚设置

功能设置

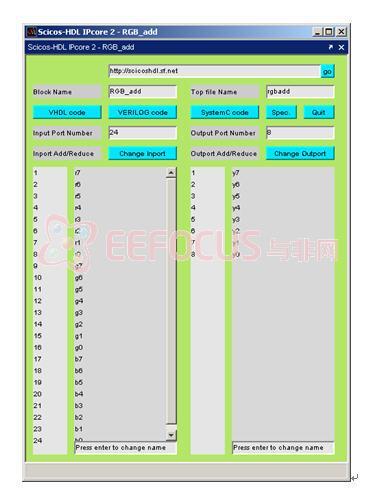

3.2.2.4RGB_ADD

计算 R分量+G分量+B分量 采用IP Core模式实现

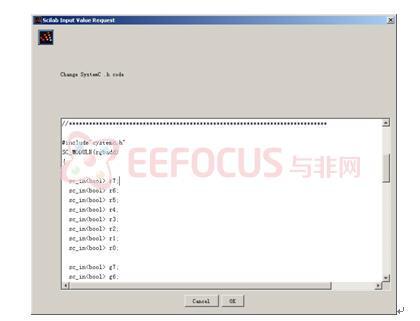

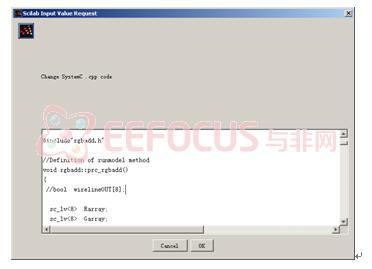

引脚设置

功能设置

功能设置

3.2.3数据比较模块

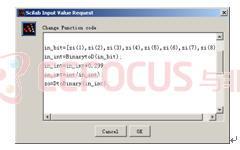

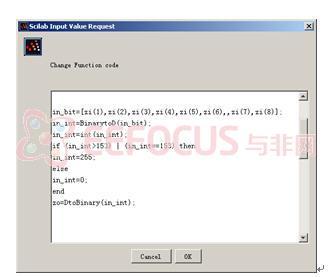

二值化元件 采用ScilabCode组合元件模式实现

引脚设置

功能设置

3.2.4输出模块

图像显示模块

3.3实验过程

3.3.1运行环境

系统软件

Scilab 5.1

Scicos-HDL 0.7 for Windows

系统硬件

Hardware:NETFPGA board

Software:Xilinx ISE Design Suite 10.1 SP3

3.3.2安装 Scilab 5.1 for Windows

在 http://www.scilab.org/ 进行下载

注意 只支持 scilab5.1 的windows版, scilab5.1以后的版本中因为Scicos改作xcos , 此版本正在开发中。

3.3.3安装Scicos-HDL

1.Download Scicos-HDL package, save it, like (

- 动态可重构系统的通信结构研究(06-06)

- 采用FPGA部分动态可重构方法的信号解调系统设计(06-05)

- 基于FPGA的动态局部可重构实现方法(06-04)

- 手持移动终端的可重构天线设计(12-20)

- 可编程模拟器件在接收机动态可重构结构应用(03-31)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)