基于NETFPGA的可重构科学计算平台

例

课题组前期与中科院自动化所中法实验室(LIAMA)和法国INRIA Scilab组织在科学计算算法转换到硬件描述语言方面有着长期合作基础,合作开发Scilab/Scicos-HDL软件系统已经数年,在开源领域有一定的知名度。本项目设计把科学计算软件与FPGA技术可重构系统相结合,构建出低成本和易于使用的高性能科学计算平台。本系统研究实现了基于FPGA可重构计算技术的科学计算平台系统原型,实现了Scilab-FPGA运算任务的协同工作,对于广大用户,整个系统透明,将其中的数学算法转换为数字电路硬件逻辑的理论方法和软件,开发与Scilab系统相互通信交互的FPGA硬件模块,实现Scilab/scicos-HDL与FPGA硬件模块联合仿真,在高性能科学计算领域,有较强的应用价值。

1.4研究意义

探索和建立数学算法向硬件逻辑转换的理论方法,对于当前的可重构计算、高速信号处理、FPGA应用设计乃至IC 设计都有着重要意义 ,其关键的问题在于给用户提供数学算法向硬件逻辑转换的工具,以此来帮助用户更加快速的建立应用。基于FPGA的可重构高性能计算将有可能大大降低对于超级计算机的需求,大量的科学计算问题将有可能提供FPGA的硬件逻辑得以实现 . 同时 ,基于FPGA的可重构高性能计算系统的硬件成本相比高性能超级计算机来说较低,更加有利于普及和推广。

2设计与实现

本章来说明对于项目整个系统的设计结构进行了说明,并且说明了目前实现的部分。

2.1总体设计

2.1.1总体设计图

系统中 Scicos-HDL模块负责 硬件电路的设计、仿真和HDL代码输出。当用户完成了一个 硬件设计后 ,可以先行在Scicos-HDL中进行软件仿真,仿真完成后,用户可以导出VHDL、Verilog、SystemC这三种硬件描述语言的代码(可综合)。导出的HDL代码经过用户手动处理,下载到NETFPGA板子上后,通过千兆以太网接口,与Scicos-HDL进行软硬件联合仿真。

在NETFPGA板子上,通过以太网连接MicroBlaze处理核心,使用HTTP协议进行数据交换Scicos-HDL导出的代码以用户自定义IP的方式加入到系统中。

2.1.2技术发展路线

本节来阐述项目技术的基本原理和发展的技术路线。

(1)数学算法转换成硬件逻辑原理

图形化的算法描述和仿真是一种常见的算法表达方式,其也最接近于实物性质的描述,目前计算机软件中采用图形化仿真方法的很多,如MatlAB,SystemView、labView等.本研究设计了一套基于硬件知识的图形化算法仿真机制,使得用户在软件中根据算法需要画出算法流程图,由系统处理后形成硬件逻辑描述,其基本的结构描述如下:

用途 | 计算机程序结构 | FPGA结构 |

加法 | + 运算 | 硬件加法器 |

乘法 | X 运算 | 硬件乘法器 |

循环结构 | FOR 循环 | 计数器 |

判断结构 | IF | 数值比较器+数据选择器 |

递增结构 | i++ | 加法计数器 |

递减结构 | i-- | 减法计数器 |

矩阵加法 | 多条程序实现 | 矩阵加法器 |

矩阵乘法 | 多条程序实现 | 矩阵乘法器v |

赋值 | 赋值语句 | 寄存器 |

功能模块 | 函数 | 算法硬件模块 |

数组 | 数组 | RAM |

计算机程序结构与FPGA程序结构对比

通过可以看出在程序设计中能够实现的程序基本结构在FPGA均有对应的硬件实现。本系统中数学算法转换成硬件逻辑是通过建立图形化运算机制基础上:添加FPGA流水线运算基本元件、使用图形化方法连接各个元件构成算法逻辑图、把算法逻辑图转换成为可综合HDL描述这三个步骤进行完成。

(2)协同工作中FPGA模块并行计算

FPGA运算与计算机运算的一个很大的区别在于FPGA中的各个运算单元都是实际硬件存在而计算机运算中的各个运算单元主要是在软件系统中建立顺序执行,因此FPGA可以实现所有运算单元的协调并行计算,但是FPGA并不能自动完成并行计算任务,这需要采用流水线技术来完成。

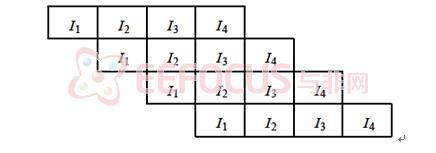

流水线处理源自现代工业生产装配线上的流水作业,是指将待处理的任务分解为相对独立的、可以顺序执行的,而又相互关联的一个个子任务.图1 是采用流水线技术的一个指令集的操作过程,我们将某一操作分为4 个子任务:取指令I1 ,译码I2 ,取操作数I3 和运算I4 ,假如每个操作执行的时间均为T ,则执行4 个操作的执行时间为4 T ,将这4 个子任务在时间上重叠,用4 个子部件来完成,相应的4 个子部件连接成串行方式,每个子部件执行的时间为T ,每隔T 时间就可输出一个操作处理结果,平均速度提高了4 倍,在加入适当的转移控制之后,即成为流水线操作的工作方式.

采用流水线技术的一个指令集的操作

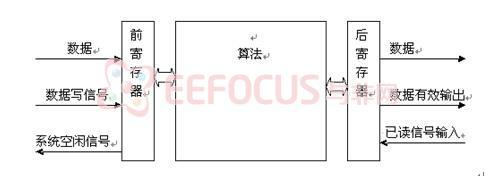

采用流水线技术,可以大大提高系统运行速度,特别适合于需要进行大批量简单运算的场合,如数字信号处理中的卷积操作、FIR 或FFT滤波器等。本研究中作为算法流程机制的FPGA模块均采用流水线结构,其基本结构如下:

基本算法流程模块

一个基本的算法流程模块采用前

- 动态可重构系统的通信结构研究(06-06)

- 采用FPGA部分动态可重构方法的信号解调系统设计(06-05)

- 基于FPGA的动态局部可重构实现方法(06-04)

- 手持移动终端的可重构天线设计(12-20)

- 可编程模拟器件在接收机动态可重构结构应用(03-31)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)