基于NETFPGA的可重构科学计算平台

寄存器和后寄存器,使得系统模块的工作只取决于自身的运算是否完成,在整体中相对独立,系统中有多个此类算法模块是独立并行工作。

(3) FPGA-PC协同科学计算

此项包含2个方面的内容:一个是FPGA算法系统中本身就有支持科学计算的算法模块;一个是FPGA运算系统可以和计算机端的科学计算系统连接起来完成FPGA-PC协同科学计算工作。

对于第一个方面本研究在系统的元件库中设置了矩阵运算元件库在完成基本的矩阵运算:矩阵运算是科学计算中的一个重要方法,要实现高性能的科学计算在系统内部就必须配置多种硬件矩阵运算处理模块,如矩阵硬件加法器、乘法器。

对于第二个问题,本研究使用netfpga硬件系统,与开源的科学计算软件Scilab进行接口,实现FPGA运算系统与科学计算系统协同工作。

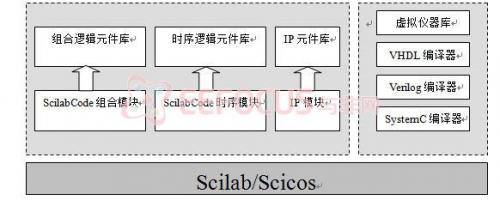

本研究中系统软件基于Scilab/Scicos开发,完成三个主要功能:

使用Scilab/Scicos进行图形化算法设计;

把图形化数学算法转换成为硬件逻辑的功能;支持 VHDL、Verilog、 SystemC 三种硬件描述语言,生成的硬件逻辑可综合;

与NETFPGA硬件系统实现 FPGA-PC协同任务运算;

2.2软件设计

软件模块的主体功能是硬件设计、仿真、输出、软硬件联合运算。

软件模块的结构如下

软件结构图

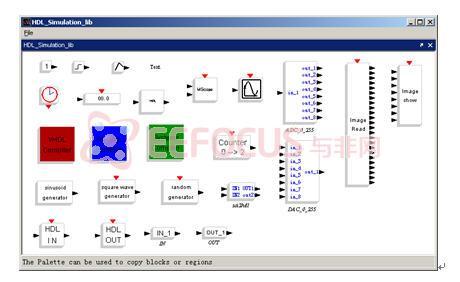

软件系统目前已经实现的有组合逻辑元件库、时序逻辑元件库、虚拟仪器库、VHDL编译器、Verilog编译器、SystemC编译器。

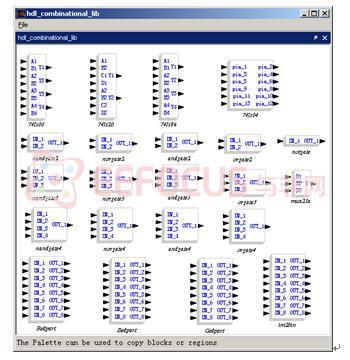

组合逻辑元件库

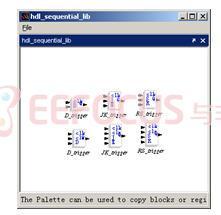

时序逻辑元件库 超级元件库

虚拟仪器库

IP 元件库

2.2.1组合逻辑元件

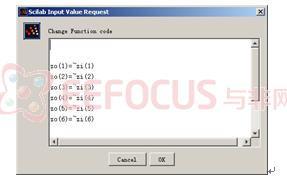

所有的组合逻辑元件,均派生自ScilabCode组合模块 ,使用者只要使用scilab 语言在ScilabCode组合模块 中定义模块功能 和 模块的引脚 ,系统会自动生成相应的硬件描述。

例如:

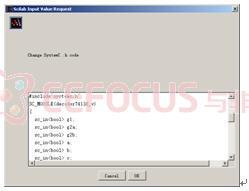

用户打开一个ScilabCode组合模块 放置于 设计区后 ,点击元件的SET菜单,弹出界面进行引脚的功能的设置:

组合逻辑元件引脚设置界面

组合逻辑元件功能设置界面(使用纯Scilab语言描述)

设置完成点击“QUIT”按钮,系统自动生成元件

组合元件 74ls04

2.2.2时序逻辑元件

所有的时序逻辑元件,均派生自ScilabCode时序模块 ,使用者只要使用scilab 语言在ScilabCode时序模块 中定义模块功能 和 模块的引脚 ,系统会自动生成相应的硬件描述。

例如:

用户打开一个ScilabCode时序模块 放置于 设计区后 ,点击元件的SET菜单,弹出界面进行引脚的功能的设置:

时序逻辑元件引脚设置界面

时序逻辑元件功能设置界面(使用Scilab语言描述,状态转换图)

设置完成点击“QUIT”按钮,系统自动生成元件

时序逻辑元件例子

2.2.3IP Core元件

所有的IP Core元件,均派生自IP Core模块 ,使用者只要在IP Core模块 中定义模块功能 和 模块的引脚 ,系统会自动生成元件。

例如:

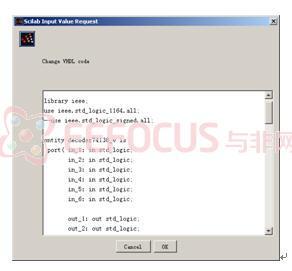

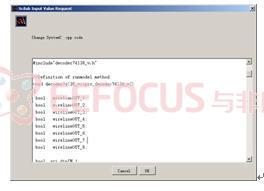

用户打开一个IP Core模块放置于 设计区后 ,点击元件的SET菜单,弹出界面进行引脚的功能的设置:

IP Core元件引脚设置界面

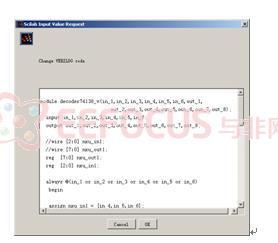

进行引脚设置以后,系统会自动生成VHDL、Verilog、SystemC这三种硬件描述语言的模板,用户根据所需功能修改模板,即可完成模块设计。

VHDL语言模板

Verilog语言模板

SystemC语言模板- 头文件

SystemC语言模板- 程序文件

编辑完成,点击:“QUIT”按钮,系统后自动完成元件的建立。

IP Core元件例子

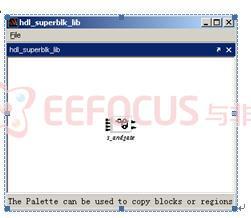

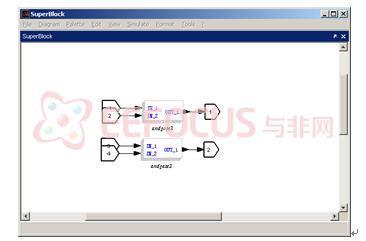

2.2.4超级模块元件

超级元件是指由多种不同的元件组合起来的元件,用户可以根据需要使用 组合逻辑元件、时序逻辑元件、IP Core元件 来建立超级元件,另外超级元件也可由数个超级元件组成。

超级元件内部

超级逻辑元件例子

2.2.5编译器模块

VHDL编译器,可以将Scicos-HDL中设计的硬件电路输出成为可综合的VHDL语言代码。

VHDL编译器,可以将Scicos-HDL中设计的硬件电路输出成为可综合的VHDL语言代码。

Verilog编译器,可以将Scicos-HDL中设计的硬件电路输出成为可综合的Verilog语言代码。

Verilog编译器,可以将Scicos-HDL中设计的硬件电路输出成为可综合的Verilog语言代码。

SystemC编译器,可以将Scicos-HDL中设计的硬件电路输出成为可综合的SystemC语言代码。

SystemC编译器,可以将Scicos-HDL中设计的硬件电路输出成为可综合的SystemC语言代码。

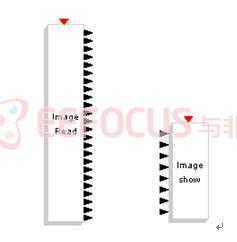

2.2.6虚拟仪器模块

虚拟仪器模块主要是针对元件电路调试和仿真中经常使用的几种元件和仪器进行虚拟化。但更多的Scicos-HDL中可以Scicos本身众多的元件作为虚拟仪器元件。

8位的ADC 与 DAC 元件

图像的读取和显示元件

示波器元件

波形发生器元件

2.2.7接口模块

接口模块至关重要,它负责了Scicos-HDL仿真引擎与 Scilab\Scicos系统仿真引擎的接口。

接口元件

2.3硬件设计

系统的硬件部分基于NETFPGA实现。

2.3.1NETFPGA

NetFPGA平台详细的组成框图如下:

NetFPGA是由美国斯坦福大学(Stanford University)开发设计的一个低成本可重用硬件平台。一个完整的NetFPGA系统由NetFPGA开发板、双口千兆以太网卡、运行于CentOS操作系统的PC机(或服务器)以及其他软件程序组成,通过各个层次软硬件

- 动态可重构系统的通信结构研究(06-06)

- 采用FPGA部分动态可重构方法的信号解调系统设计(06-05)

- 基于FPGA的动态局部可重构实现方法(06-04)

- 手持移动终端的可重构天线设计(12-20)

- 可编程模拟器件在接收机动态可重构结构应用(03-31)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)