基于NETFPGA的可重构科学计算平台

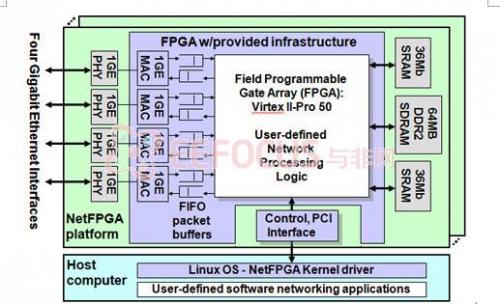

的互相配合完成复杂的网络结构测试。其中NetFPGA开发板是整个平台的核心,为用户提供了及其丰富的硬件资源。

核心部分是一个Xilinx公司的Virtex-II Pro 50型FPGA,这个比较大的FPGA由用户自定义的逻辑来编程,其核心时钟频率为125 MHz。另外还有一个小的Xilinx Spartan型FPGA用来实现连接主机处理器的PCI接口的控制逻辑。

在外部存储器方面,两片4.5MB的Cypress公司SRAM与FPGA核心逻辑同步运行于125 MHz时钟频率,字长36比特。总共64 MB的两片Micron公司DDR2型SDRAM与FPGA异步运行,其时钟频率为200MHz,字长32比特,存储带宽400 M字/秒(12,800Mb/s)。

在外部接口方面,除了连接PC主机的PCI总线插口,一个Broadcom公司的物理层收发器(PHY)包含了四个千兆位以太网接口,使该平台可以连接四根标准的category 5、category 5e、或category 6以太网双绞线来收发数据分组,并组成网络拓扑;四端口的PHY内部连接着作为FPGA软核的四个千兆位以太网MAC控制器。此外,两个SATA连接口使得系统内部的多个NetFPGA可以通过SATA数据线连接起来,互相之间直接以很高的速度交换数据,而不必再通过PCI总线。

NetFPGA通过PCI总线与主机CPU连接,提供了硬件加速的数据通道,分担CPU的处理任务。主机CPU按照DMA方式读写NetFPGA上的寄存器和存储器来配置NetFPGA的工作模式,并对NetFPGA的工作状态进行监控。

此外,双口千兆以太网卡用来给主机提供本地网络接口,并与NetFPGA连接,实现特殊的用法。

NetFPGA平台的组成框图

NetFPGA开发板的主要硬件组成:

Xilinx Virtex-II Pro 50 FPGA

内嵌两颗高性能PowerPC处理器

国际通用的JTAG测试端口

4.5 MB高速静态随机存取器

内嵌64MB二代内存

4组速率高达1Gbps的标准以太网接口

支持 Cat5E和Cat6标准电缆

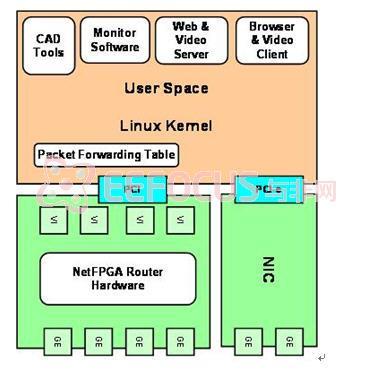

NetFPGA系统框图:

2.3.2硬件结构

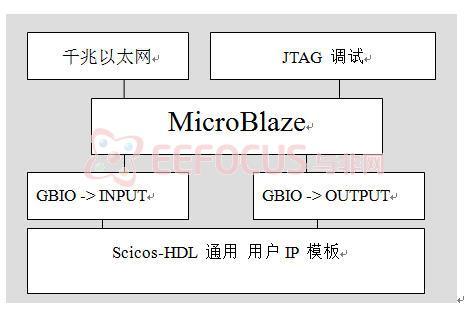

硬件部分基于NETFPGA的硬件,主体结构如下图:

基于NETFPGA的硬件结构图

以MicroBlaze为核心,千兆以太网作为与PC交互接口,Scicos-HDL输出的代码,用户手动添加到 用户自定义模块中 ,完成硬件部署。

由于NETFPGA系统基于LINUX,所以本设计采用了一个外部的 XILINX Platform Cable USB设备,进行下载与调试的工作,使得NETFPGA硬件能够独立工作。

NETFPGA硬件连接图

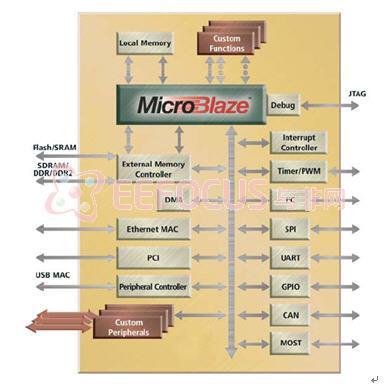

2.3.3微处理器

MicroBlaze 是基于Xilinx公司FPGA的微处理器IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze 处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其的数据。

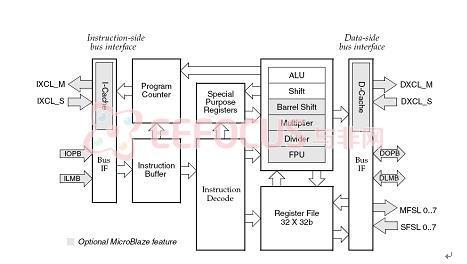

Micro Blaze处理器采用RISC架构和哈佛结构,32位地址总线,独立的指令和数据缓存,并且有独立的数据和指令总线连接到IBM的OPB总线,使得它能很容易和其它外设IP核一起完成整体功能。图3.2.2显示了MicroBlaze的接口连接和架构布局,图3.2.3显示了MicroBlaze的内部功能块图。

MicroBlaze的接口连接和架构布局

MicroBlaze内部的功能块图

(1)内部结构

MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—PC指针和MSR状态标志寄存器。为了提高性能,MicroBlaze还具有指令和数据缓存。所有的指令字长都是32位,有3个操作数和2种寻址模式。指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。指令执行的流水线是并行流水线,它分为3级流水:取指、译码和执行,如图2所示。

(2)存储结构

MicroBlaze是一种大端存储系统处理器,使用如图3所式的格式来访问存储器。

(3)中断控制和调试接口

MicroBlaze可以响应软件和硬件中断,进行异常处理,通过外加控制逻辑,可以扩展外部中断。利用微处理器调试模块(MDM)IP核,可通过JTAG接口来调试处理器系统。多个MicroBlaze处理器可以用1个MDM来完成多处理器调试。

(4)快速单一连接路接口

MicroBlaze处理器具有8个输入和8个输出快速单一链路接口(FSL)。FSL通道是专用于单一方向的点到点的数据流传输接口。FLS和MicroBlaze的接口宽度是32位。每一个FSL通道都可以发送和接收控制或数据字。

应用EDK(嵌入式开发套件)可以进行MicroBlaze IP核的开发。工具包中集成了硬件平台生产器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。EDK中提供一个集成开发环境XPS(Xilinx平台工作室),以便使用系统提供的所有工具,完成嵌入式系统开发的整个流程。

- 动态可重构系统的通信结构研究(06-06)

- 采用FPGA部分动态可重构方法的信号解调系统设计(06-05)

- 基于FPGA的动态局部可重构实现方法(06-04)

- 手持移动终端的可重构天线设计(12-20)

- 可编程模拟器件在接收机动态可重构结构应用(03-31)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)