善用Vivado工程配置文件xpr快速工程创建

<Option Name="Part" Val="xc7a50tftg256-1"/>

</Configuration>

</Project>

注意,这里我们只需要改2个地方,即上面代码里面红色字体部分:

1. Path="D:/datasheet/xilinx/XDDR_PRJ/xddr_prj.xpr"这个表示工程存放路径,大家可以把自己的工程存放路径放上去覆盖它,注意是“/”,而windows的路径都是“\”。

2. Val="xc7a50tftg256-1"表示所使用的FPGA器件型号,大家也可以使用自己的器件覆盖上去。

比如,特权同学这里只修改了路径,使用一样型号的FPGA型号。那么修改如下。

<?xml version="1.0" encoding="UTF-8"?>

<!-- Product Version: Vivado v2016.2 (64-bit) -->

<!-- -->

<!-- Copyright 1986-2016 Xilinx, Inc. All Rights Reserved. -->

<Project Version="7" Minor="14" Path="D:/datasheet/xilinx/XADC_PRJ/xadc_prj.xpr">

<DefaultLaunch Dir="$PRUNDIR"/>

<Configuration>

<Option Name="Id" Val="0fd604fa43664afbb4172d9765411c21"/>

<Option Name="Part" Val="xc7a50tftg256-1"/>

</Configuration>

</Project>

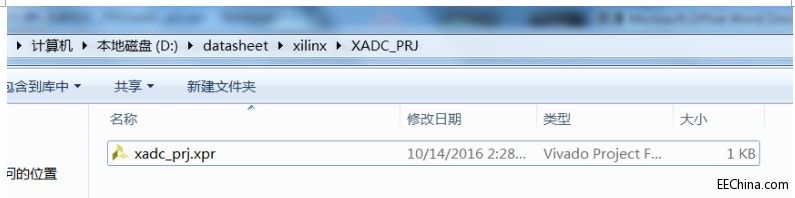

如图所示,不要忘记吧xadc_prj.xpr文件放置到脚本中设置的路径下。

双击xadc_prj.xpr,Vivado工具将被打开,会自动以此创建新的工程,界面如图所示。

此时,工程文件夹里也自动创建了很多新的子文件夹。

当然了,在xadc_prj.xpr文件里,也平白无故的增加了一大堆新的配置信息,这都归功于Vivado自动配置功能。

这里只是举个xpr文件做工程移植的最简单例子,算是抛砖引玉,大家可以自己根据需要定制自己的移植配置文件,这对于要多次创建基于同一个FPGA器件平台的工程而言,非常高效。这其实也是脚本开发相对于GUI开发方式的一个主要优势。

Xilinx ModelSim Verilog FPGA ADC 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)