例说FPGA连载50:NAND Flash实例之功能概述

时间:11-21

来源:互联网

点击:

例说FPGA连载50:NAND Flash实例之功能概述

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

本实例在工程实例3的基础上,添加了一个自定义的NAND Flash控制器组件,如图6.1所示,这个组件也是挂在Qsys系统的Avalon-MM总线上。NAND Flash复杂的底层驱动时序都由这个控制器内部产生,无需NIOS II处理器直接参与。NIOS II处理器只需要通过Avalon-MM总线对相关寄存器进行读写就可以实现NAND Flash的读写。

图6.1 工程实例4系统框图

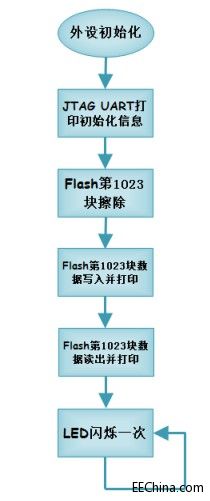

在搭建的这个Qsys平台上,我们需要运行一个简单的NAND Flash擦除、写入和读出的操作。软件流程如图6.2所示,在外设初始化后,通过JTAG UART打印一串初始化信息;接着依次对NAND Flash的第1023块(Block)存储区执行擦除、写入操作,同时打印所有写入数据和读出数据进行比较;完成以上操作后,LED闪烁。

图6.2 工程实例4软件流程图

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)