例说FPGA连载67:AV视频采集之移位寄存器概述

时间:01-15

来源:互联网

点击:

例说FPGA连载67:AV视频采集之移位寄存器概述

特权同学,版权所有

在很多涉及迭代运算的应用中,常常需要用到移位寄存器来帮助完成功能的实现。而使用FPGA既有的逻辑资源来实现寄存器虽然也很简单,若是位宽和深度不大时倒也是个不错的解决方案,但对于大深度大位宽的应用可就无法应付了。因此,我们更多的会用到FPGA片内的存储器资源来实现移位寄存器的功能。

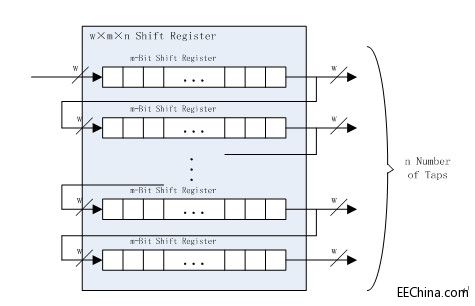

使用片内存储器实现移位寄存器的接口如图12.11所示,其可配置的参数有:一个位宽为w的移位输入数据和相同位宽的移位输出数据,一个输入时钟信号(图中未示意)作为数据移入或者移出的同步信号,可选的时钟使能输入信号和异步清除输入信号(图中未示意)。还有一个寄存器深度taps,它可以是一组信号,也可以是好多个小信号。

图12.11 FIFO内部结构示意图

这个移位寄存器的使用其实很简单。配置输入输出的数据位宽w,移位寄存器的一个taps位宽m,总的taps数量n(相当于数据深度)。这三个参数乘积就是占用的移位寄存器的存储大小。每个时钟周期输入一个移位数据shift_in_data,同时输出一个数据shift_out_data,而存储器内部则是每个clk周期移位一次,每个tap的输出直接移位到下一个tap的输入。每个tap的最后一个w位宽的数据都能出现在对外接口中供使用。

FPGA 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)