基于至简设计法的数字时钟设计

基于至简设计法的数字时钟设计

明德扬科技教育有限公司

官 网:www.mdy-edu.com

淘 宝:mdy-edu.taobao.com

QQ 群:97925396

至简设计法数字时钟视频链接:http://www.mdy-edu.com/article_cat/video?id=20

数字时钟是常见的毕业设计题目。我们做毕业设计时,一般使用数码管来显示数字。小时、分钟和秒钟各两位数字,所以需要用到6位的数码管。

如果平时不动手,要做这个毕业设计,很多人都会觉得挺难的。收集到的代码,其风格也是五花八门,第一感觉是貌似能看懂,但就是不知道怎么设计出来的。

其实如果有正确的设计思路和方法,其实现起来是非常简单的。下面我们就核心的数字模块为例,讲解如何使用至简设计法来实现。

数字模块的功能,是产生6个信号,分别表示时十位、时个位、分十位、分个位、秒十位和秒个位的值。例如上述信号值依次为2、1、4、3、5、9时,则表示时间为21点43分59秒。

仔细观察6个信号,每个单独来看,其数字都是递增的,增加到一定数后就清零。以秒个位为例,开始时值为0,然后是1、2、3依次增加,直到变成9后,然后变成0,再次循环。其他信号都是相同的规律。这些依次递增的信号,就是计数器。

我们认识到这些信号是计数器,那就好办了,明德扬最擅长就是计数器的设计。计数器设计只需要考虑两点,什么时候加1和要数多少个,明确这两个问题后,剩下的就是套用明德扬计数器模板了。

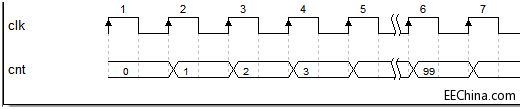

以秒个位这个计数器为例,这个计数器加1的条件是什么呢?到了1秒就加1。那我们怎么知道1秒钟时间到了呢?FPGA是通过数时钟周期数来确定时间的。例如下图,假设时钟频率是50MHz,即时钟周期是20ns,cnt是每个时钟加1,则当cnt==99时,就说明数了100个时钟周期,也就是时间是100*20=2000ns了。

同样的道理,1秒钟时间,我们就是数1s/20ns= 50_000_000个时钟周期。我们也认识到这个cnt也是计数器,其加1条件是“1”,要数50_000_000个数。我们套用明德扬计数器模块,即有下面代码。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 | always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt <= 0; end else if(add_cnt)begin if(end_cnt) cnt <= 0; else cnt <= cnt + 1; end end assign add_cnt = 1 ; assign end_cnt = add_cnt && cnt== 50_000_000-1; |

代码中,always语句除了名字后,完全套用模板,不用更改。加1条件体现在第13行,要数多少个体现在第14行。

确定了cnt后,那么秒个位的加1条件就非常明确了,就是cnt数到50_000_000个,也就是end_cnt有效的时候。所以秒个位的加1条件是end_cnt。

秒个位要数多少个数字呢?由0到9,因此有10个。

综上所述,我们得到秒个位的代码如下表。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 | always@(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin miao_g <= 0; end else if(add_miao_g)begin if(end_miao_g) |

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)