赛灵思 SDSoC 开发环境介绍

时间:03-11

来源:互联网

点击:

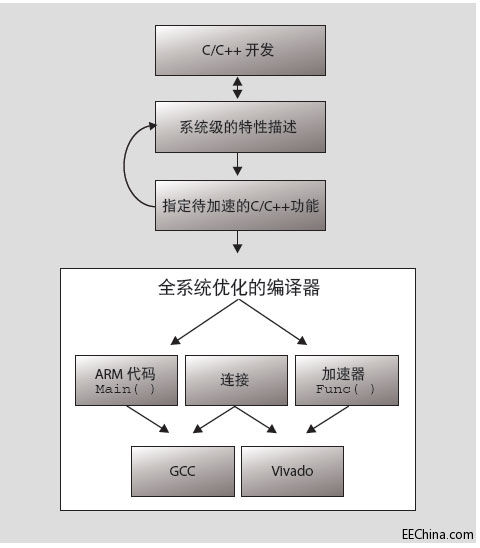

全系统优化的编译器

SDSoC 还具有针对ARM 处理系统和可编程逻辑的全系统优化的编译器。SDSoC 旨在帮助系统架构师和软件团队使用“golden

C/C++ source”,通过生成最佳系统连接,快速完成宏架构和微架构的配置。这样既能得到最佳系统连接和存储器接口,还能快速完成设计空间探索,便于开发人员综合权衡性能、吞吐量、时延,同时保持较短的设计迭代时间。

该编译器充分利用基础的高层次综合编译器技术,已有逾千名编程人员使用该技术生成了基于C/C++ 的高性能IP。将该编译器与链接器结合使用,并基于目标平台以及在可编程逻辑中生成的用户指定的自动软件加速功能,将程序转换到完整的软硬件系统中。

基于程序语法、程序分析、调度安排、系统连接的特性化硬件建模,SDSoC 能在可编程逻辑中生成用于软件的加速器。SDSoC 充分利用平台的板支持包(BSP)、目标软件加速功能、IP 和优化库及系统连接生成功能,构建设计的可编程逻辑部分。该编译器可自动把系统编译为完整的软硬件系统,包括用于可编程逻辑的比特流和用于配置目标平台的ARM 处理系统ELF 文件。

可编程逻辑中每个加速功能都可以作为独立的线程运行。SDSoC 可生成与之同步和保存原始程序语义所需的软硬件组件,同时可实现任务级的并行和用流水线实现的通信和计算,以获取高性能。

C/C++ 应用源码可包含多个加速功能,特定功能的多个实例以及对主程序各不同部分中的加速器功能的调用。为获得最佳性能,SDSoC 还提供赛灵思优化库和赛灵思联盟成员提供的备选库。

通过从“single golden source”生成完整的嵌入式应用,SDSoC 可在应用层重构C/C++ 代码,便于软件开发人员迭代设计和架构变更,从而显著缩短在平台上运行工作程序所需的时间。

面向平台开发人员的专家级使用模型

SDSoC可为系统架构师和平台开发人员提供专家级的使用模型。通过将系统级的特性描述和性能分析功能与自动系统连接生成功能完美结合,该工具可帮助架构师定义、探索并生成各种架构,为自己的应用平台找到最为理想的设计实现方案,并传递给嵌入式软件开发人员,用于在应用平台顶层构建完整的应用。

借助自动系统连接生成功能,架构师可以快速定义、探索并生成宏系统架构和微系统架构,用以确定Zynq处理系统、存储器和基于可编程逻辑的加速器之间的最佳互联架构。

将赛灵思Vivado® 设计套件与SDSoC 结合运用,可用于创建特定应用平台。该平台创建功能还能够将现有的RTL 和IP 配置用作C 语言可调用的库。这对需要借助设计重用来加快平台开发的团队大有裨益。

SDSoC 可为基于Zynq 全可编程 SoC 的开发板(诸如ZC702、ZC706 等)、第三方和特定市场平台(BSP)(如Zedboard、MicroZed 和ZYBO),以及视频成像开发套件等提供板支持包(BSP)。这些BSP 中包含的元数据可让SDSoC 进行平台抽象,以便嵌入式软件开发人员和系统架构师提升生产力,并加速产品开发进程。

SDSoC 开发环境可提供类似ASSP 的C/C++ 编程体验,以提高应用开发、系统架构定义和平台创建的生产效率。 SDSoC 结合Zynq 全可编程SoC 和MPSoC,使嵌入式软件开发人员能够加快智能系统开发进程。

结论

SDSoC 开发环境可提供类似ASSP 的C/C++ 编程体验,以提高应用开发、系统架构定义和平台创建的生产效率。 SDSoC 结合Zynq 全可编程SoC 和MPSoC,使嵌入式软件开发人员能够加快智能系统开发进程。

物联网 SoC FPGA PSoC ARM 赛灵思 硬件工程师 VHDL Verilog 嵌入式 Linux 总线 相关文章:

- 采用Altera 10代FPGA实现低延时小尺寸设计(06-09)

- 为何使用Zynq SoC可以让企业产品利润激增?(09-15)

- 零基础学FPGA (一) 关于我和FPGA(01-14)

- 赛灵思最新发布的UltraScale+16nm系列FPGA、3D IC和MPSoC介绍(03-04)

- Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势(04-13)

- Xilinx 客户塑造美好的未来(09-07)