FPGA入门:第一个工程实例之设计输入

FPGA入门:第一个工程实例之设计输入

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

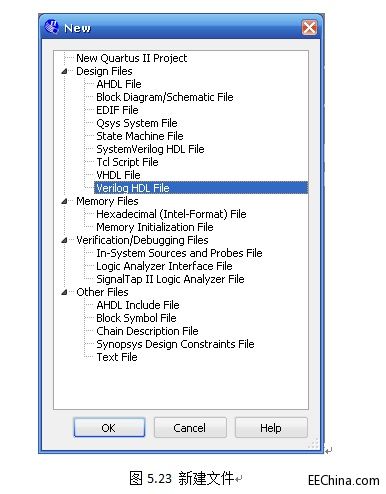

下面我们就来创建工程顶层文件,我们可以点击菜单栏的FileàNew…,然后弹出如图5.23所示的新建文件窗口,在这里我们可以选择各种需要的设计文件格式。可以作为工程顶层设计文件的格式主要在Design Files类别下,我们选择VerilogHDL File(或者VHDL File)并单击OK完成文件创建。

图5.23 新建文件

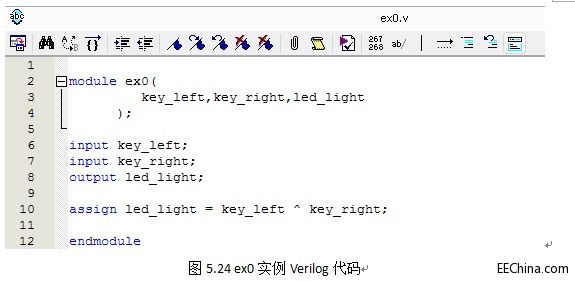

在主编辑窗口中,出现了一个新建的空白的可编辑文件,我们接着在该文件中输入实现实验功能的一段Verilog代码(如果是新建VHDL文件则对应输入VHDL代码),如图5.24所示。

图5.24 ex0实例Verilog代码

★ 代码讲解

L2/L12:固定用法申明模块,该模块命名为ex0。

L3:将该模块所有输入输出信号列表。

L6:左键输入键值采样信号。

L7:右键输入键值采样信号。

L8:LED指示灯输出信号。

L10:异或运算,使得两个按键和指示灯的关系与表5.1的真值表相吻合。

如果使用VHDL输入,则对应的VHDL代码如图5.25所示。

图5.25 ex0实例VHDL代码

在这个刚创建的Verilog(或VHDL)文件中输入代码后,快捷键Ctrl+S或点击FileàSave后则会弹出一个对话框提示输入文件名和保存路径,默认文件名会和我们所命名的module名(或entity名)相一致,默认路径也会是当前的工程文件夹。我们通常也都采用默认设置进行保持即可。

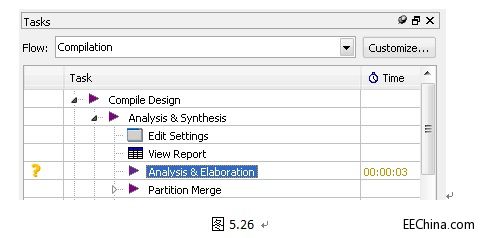

自此,我们的工程创建和设计输入工作已经完成。但是为了验证一下设计输入的代码的基本语法是否正确,可以点击Flow à Compilation下的Analysis & Elaboration按钮,如图5.26所示。同时我们可以输出打印窗口的Processing里的信息,包括各种warning和Error。Error是不得不关注的,因为Error意味着我们的代码有语法错误,后续的编译将无法继续;而warning则不一定是致命的,但很多时候warning中暗藏玄机,很多潜在的问题都可以从这些条目中寻找到蛛丝马迹。当然了,也并不是说一个设计编译下来就不可以有warning,如果设计者确认这些warning符合我们的设计要求,那么可以忽略它。

图5.26

最后,在Analysis & Elaboration完成后,通常前面的问号会变成勾号,表示通过。

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

FPGA CPLD Verilog VHDL LED 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)